#### 9400 SERIES MACROLOGIC\*

#### COMPOSITE DATA SHEET

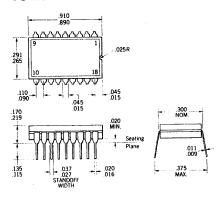

GENERAL DESCRIPTION - Fairchild 9400 Series TTL Macrologic utilizes advanced Schottky technology to provide high performance peripheral and processor oriented LSI. The design of 9400 ensures maximum design flexibility with no loss of performance. The Macrologic elements may be used with any bit length, instruction set or organization. Devices may be expanded with little or no extra components. Where applicable, bus oriented, three state outputs are provided. A new slim 24 pin package reduces PC board real estate by a third.

#### **FEATURES**

- 150-250 GATE COMPLEXITY

- COMPATIBLE WITH ALL TTL FAMILIES

- PERFORMANCE EQUIVALENT TO SCHOTTKY IMPLEMENTATION

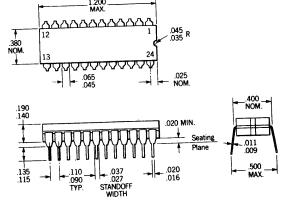

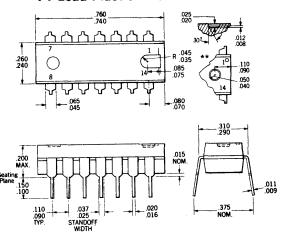

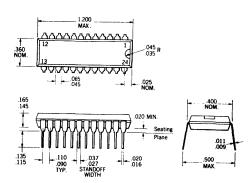

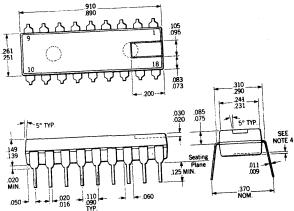

- 14, 16, 18, and SLIM 24 PIN PACKAGES

- INPUTS ABOUT 1/4 NORMAL TTL LOAD, i.e.,  $360-400~\mu A$

- OUTPUTS DRIVE 16 MA (10 U.L.) OR 8 MA (5 U.L.) DEPENDING ON APPLICATION

- DESIGNED FOR MAXIMUM FLEXIBILITY

- OPERATE OVER COMMERCIAL OR MILITARY TEMPERATURE RANGE

#### ADVANCED SCHOTTKY PROCESS

The 9400 family uses an advanced Schottky TTL process to obtain the best speed/power product of any commercially available digital bipolar circuitry. Key characteristics are as follows:

- ullet SHALLOW, LOW CAPACITANCE DIFFUSION TO PROVIDE TRANSISTOR  $\mathbf{F}_{\mathsf{T}}$  or 2 GHz

- SCHOTTKY DIODES TO ELIMINATE STORAGE TIME

- INTERNAL GATES

- 30 MILS (50 GATES PER MM)

- 3.5 NS DELAY

- 6 pJ DELAY POWER PRODUCT

- OUTPUT BUFFERS

- 70 MILS

- 5 NS DELAY

- 10 pJ DELAY POWER PRODUCT

<sup>\*</sup>A Trademark of Fairchild Camera and Instrument Corporation.

# TABLE OF CONTENTS

|                                                      | Page             |

|------------------------------------------------------|------------------|

| General Description                                  | 1                |

| Table of Contents                                    | 2                |

| Definition of Symbols                                | 3 <del>-</del> 5 |

| Recommended Operating Conditions                     | 6                |

| Absolute Maximum Ratings                             | 6                |

| Data Sheets                                          | -                |

| 9401 Cyclic Redundancy Check (CRC) Generator/Checker | 7-13             |

| 9403 Serial/Parallel FIFO                            | 14-31            |

| 9404 Data Path Switch (DPS)                          | 32-39            |

| 9405 Arithmetic Logic Register (ALRS)                | 40-49            |

| 9406 P-Stack                                         | 50-73            |

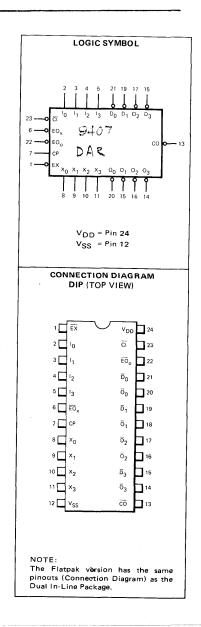

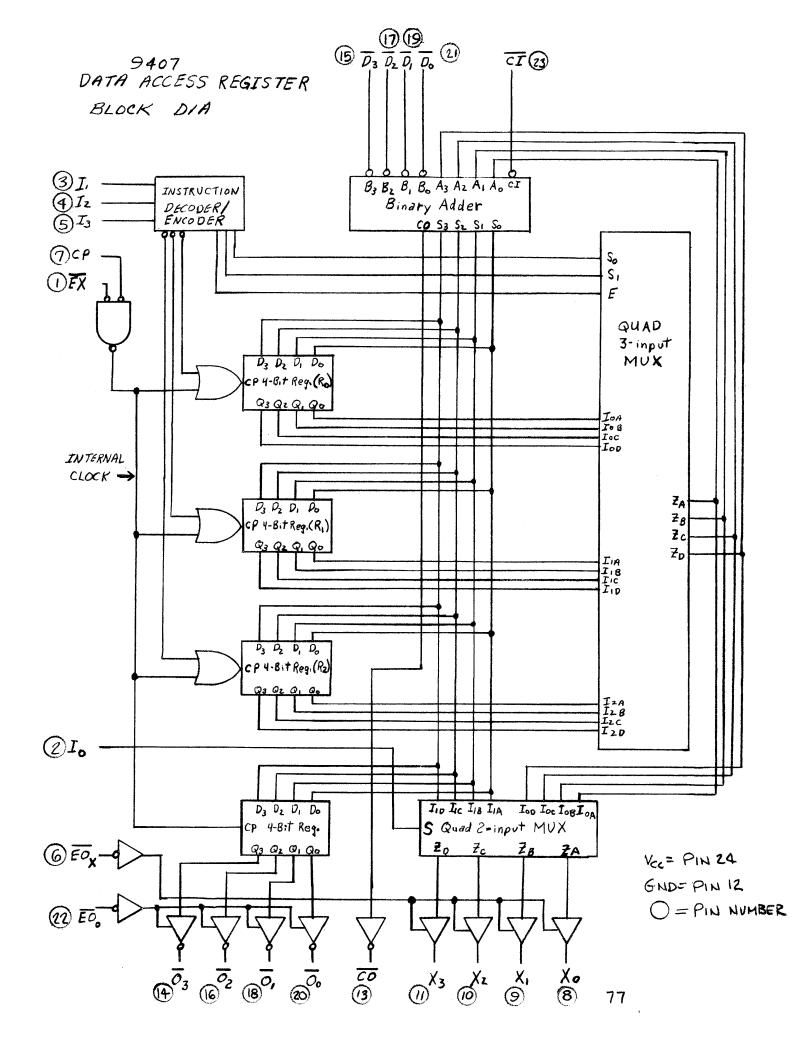

| 9407 Data Access Register (DAR)                      | 74-82            |

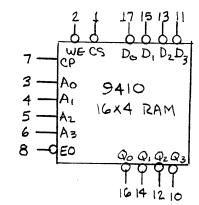

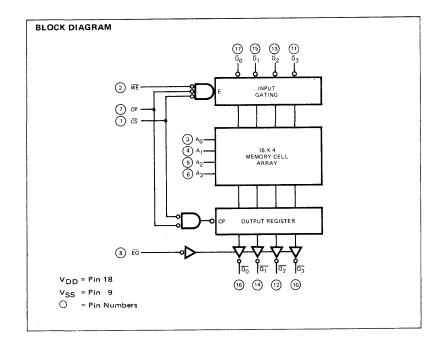

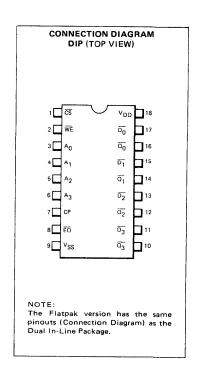

| 9410 16 X 4 Clocked RAM                              | 83-87            |

| Ordering Information                                 | 87               |

| Packaging                                            | 88-89            |

#### DEFINITION OF SYMBOLS AND TERMS USED IN THIS DATA SHEET

CURRENTS - Positive current is defined as conventional current flow into a device. Negative current is defined as conventional current flow out of a device.

1<sub>1H</sub> High-level input current.

The current flowing into an input when a specified high-level voltage is applied to that input.

1<sub>11</sub> Low-level input current.

The current flowing into an input when a specified low-level voltage is applied to that input.

- $^{1}\mathrm{OH}$  High-level output current. The current flowing into the output with a specified high-level output voltage  $\mathrm{V}_{\mathrm{OH}}$  applied.

- Low-level output current. The current flowing into the output with specified low level output voltage  $V_{\rm Ol}$  applied.

- $1_{OS}$  Short-circuit output current.

The current flowing into an output when that output is short-circuited to ground (or other specified potential) with input conditions applied to establish the output logic level farthest from ground potential (or other specified potential).

$1_{OZH}$  Output off current high.

The current flowing into a disabled three state output with a specified high level output voltage  $\mathbf{V}_{\mathsf{OH}}$  applied.

$1_{OZL}$  Output off current low.

The current flowing into a disabled three state output with a specified low level output voltage  $V_{\mbox{OL}}$  applied.

1<sub>CC</sub> Supply current.

The current flowing into the  $V_{CC}$  supply terminal of a circuit when the inputs are open.

VOLTAGES - All voltages are referenced to Ground.

$V_{1H}$  Input high voltage.

The range of input voltages that represents a logic HIGH level in the system.

V<sub>1L</sub> Input low voltage.

The range of input voltages that represents a logic LOW level in the system.

$V_{1H}$ (min) Minimum input high voltage.

The minimum allowed input HIGH level in a logic system.

V<sub>11</sub> (max) Maximum input low voltage.

The maximum allowed input LOW level in a system. Output high voltage.

$v_{OH}$  The range of voltages at an output terminal for specified output current  $I_{OH}$ . Device inputs are conditioned to establish a HIGH level at the output.

$V_{OL}$  Output low voltage.

The range of voltages at an output terminal for specified output current  $\mathbf{I}_{0L}$ . Device inputs are conditioned to establish a LOW level at the output.

V<sub>CD</sub> Input clamp diode voltage.

The range of negative voltage applied to an input which will cause -18 ma to flow into the device.

V<sub>CC</sub> Supply voltage.

Typically 5 volts.

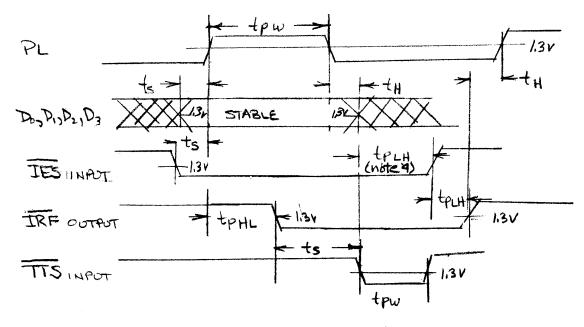

#### AC SWITCHING PARAMETERS.

$f_{MAX}$  Toggle frequency/operating frequency.

The maximum rate at which clock pulses may be applied to a sequential circuit. Above this frequency the device may cease to function.

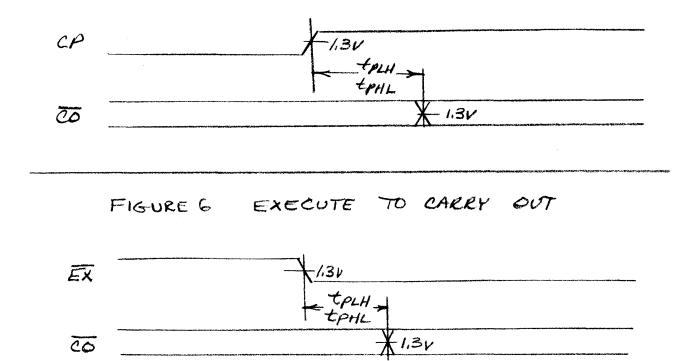

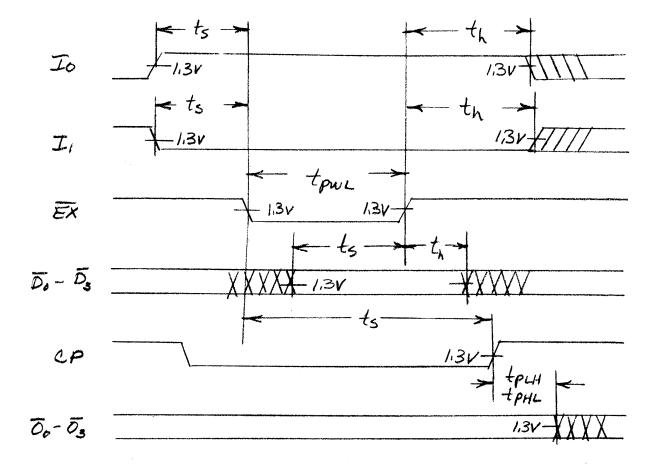

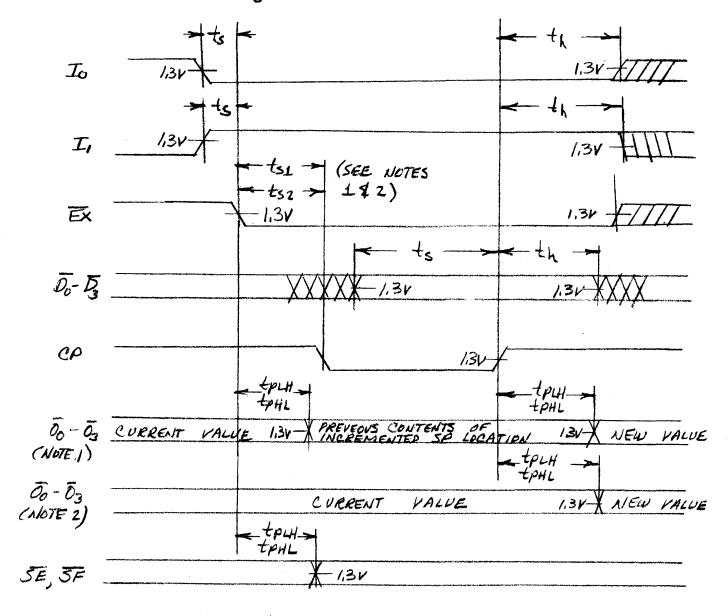

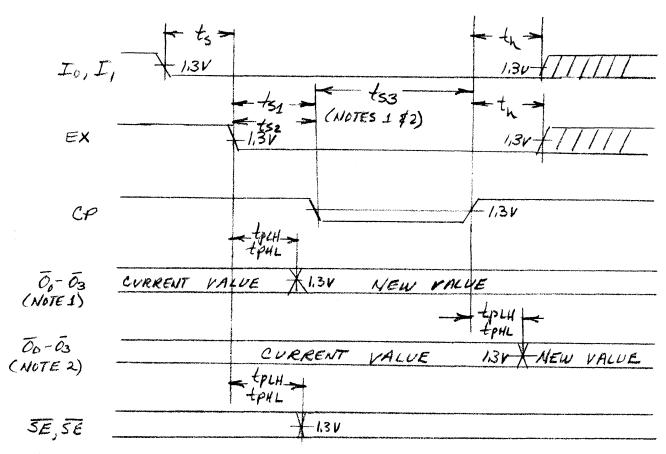

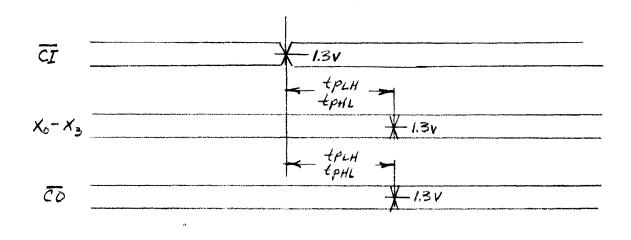

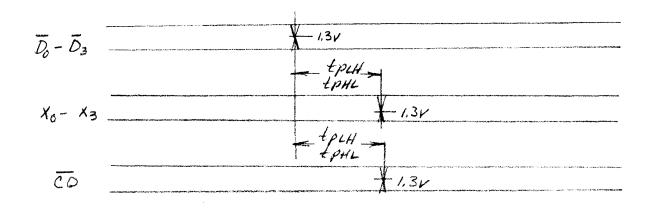

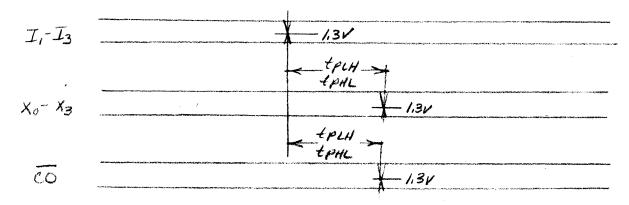

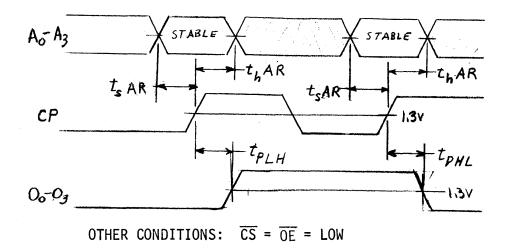

t<sub>PLH</sub> Propagation delay time.

The time between the specified reference points, normally 1.3 volts on the input and output voltage waveforms, with the output changing from the defined LOW level to the defined HIGH level.

${\rm t_{PHL}}$  Propagation delay time.

The time between the specified reference, normally 1.3 volts on the input and output voltage waveforms, with the output changing from the defined HIGH level to the defined LOW level.

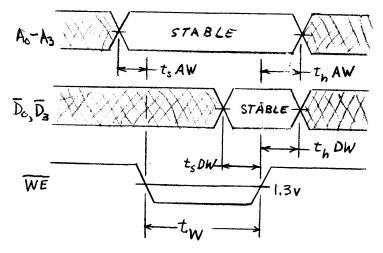

t<sub>W</sub> Pulse Width.

The time between 1.3 volt amplitude points on the leading and trailing edges of pulse.

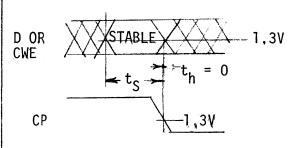

t<sub>h</sub> Hold time.

The interval immediately following the active transition of the timing pulse (usually the clock pulse) or following the transition of the control

input to its latching level, during which interval the data to be recognized must be maintained at the input to ensure its continued recognition. A negative hold time indicates that the correct logic level may be released prior to the active transition of the timing pulse and still be recognized.

t<sub>s</sub> Set-up time.

The interval immediately preceding the active transition of the timing pulse (usually the clock pulse) or preceding the transition of the control input to its latching level, during which interval the data to be recognized must be maintained at the input to ensure its recognition. A negative set-up time indicates that the correct logic level may be initiated sometime after the active transition of the timing pulse and still be recognized.

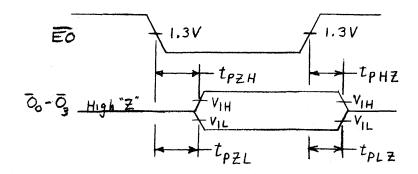

t<sub>PH7</sub> Output disable time (of a three-state output) from high level.

The time between the 1.3 volt levels on the input and output voltage. waveforms with the three-state output changing from the defined high level to a high-impedence (off) state.

t<sub>PLZ</sub> Output disable time (of a three-state output) from low level.

The time between the 1.3 volt levels on the input and output voltage waveforms with the three-state output changing from the defined low level to a high-impedance (off) state.

t<sub>PZH</sub> Output enable time (of a three-state output) to a high level.

The time between the 1.3 volt levels of the input and output voltage waveforms with the three-state output changing from a high impedance (off) state to a high level.

t<sub>P7L</sub> Output enable time (of a three state output) to a high level.

The time between the 1.3 volt levels of the input and output voltage waveforms with the three-state output changing from a high impedance (off) state to a low level.

t<sub>REC</sub> Recovery time.

The time between the 1.3 volt levels of inputs which will allow the device to operate correctly.

#### RECOMMENDED OPERATING CONDITIONS

| PARAMETER                            |     | XM  |     |      | ХC  |      |       |

|--------------------------------------|-----|-----|-----|------|-----|------|-------|

|                                      | MIN | TYP | MAX | MIN  | TYP | MAX  | UNITS |

| Supply Voltage V <sub>CC</sub>       | 4.5 | 5.0 | 5.5 | 4.75 | 5.0 | 5.25 | V     |

| Operating Free Air Temperature Range | -55 | 25  | 125 | 0    | 25  | 75   | °C    |

D for Ceramic Dip, P for Plastic Dip.

#### ABSOLUTE MAXIMUM RATINGS (above which the useful life may be impaired)

Storage Temperature Temperature (Ambient) Under Bias

VCC Lead Potential to Ground Lead

\*Input Voltage (dc)

\*Input Current (dc)

Voltage Applied to Outputs (Output HIGH)

Output Current (dc) (Output LOW)

$-65^{\circ}$ C to  $+150^{\circ}$ C

-55°C to +125°C

-0.5 V to +7.0 V

-0.5 V to + **/5** V

-30 mA to +5.0 mA

-0.5 V to  $+V_{CC}$

+30 mA

<sup>\*</sup>Either Input Voltage limit or Input Current limit is sufficient to protect the inputs.

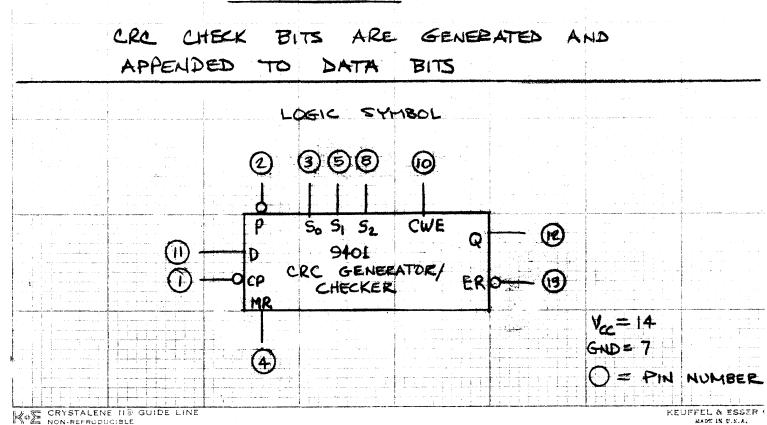

# FAIRCHILD MACROLOGIC\* ◆ 9401 CRC GENERATOR/CHECKER

Description: The 9401 Cyclic Redundancy Check (CRC) Generator/Checker provides an advanced tool for the implementation of the most widely used error detection scheme in serial digital data handling systems. A 3-bit control input selects one of eight generator polynomials. The list of polynominals includes CRC-16 and CRC-CCITT as well as their reciprocals (reverse polynomials). Automatic right justification is incorporated for polynomials of degree less than 16. Individual clear and preset inputs are provided for floppy disc and other applications. The ERROR output indicates whether or not a transmission error has occured. Another control input inhibits feedback during check word transmission. The 9401 is a member of Fairchild's Macrologic family and is fully compatible with all TTL families.

## Typical Applications

- Floppy and other disc storage systems.

- Digital cassette & cartridge systems.

- Data communication systems.

#### Features

- Guaranteed 12 MHz data rate.

- 8 selectable polynomials.

- Error indicator.

- Separate Preset & Clear controls.

- Automatic right justification.

- Fully compatible with all TTL logic families.

- 14-pin package.

<sup>\*</sup>A Trademark of Fairchild Camera and Instrument Corporation.

| LEAD NAMES      |                                                  | Loading<br>HIGH (U.L.) | (note a)<br>LOW (U.L.) |

|-----------------|--------------------------------------------------|------------------------|------------------------|

| $s_0, s_1, s_2$ | Polynomial Select Inputs                         | 0.5                    | .23                    |

| D               | Data Input                                       | 0.5                    | .23                    |

| CP              | Clock (operates on HIGH to LOW transition) Input | 0.5                    | .23                    |

| CWE             | Check Word Enable (active LOW) input             | 0.5                    | .23                    |

| P               | Preset (active LOW) input                        | 0.5                    | .23                    |

| MR              | Master Reset (active HIGH) input                 | 0.5                    | .23                    |

| Q               | Data Output                                      | 10                     | 5 (note b)             |

| ER              | Error (active HIGH) output                       | 10                     | 5 (note b)             |

NOTES:

a. 1 TTL Unit Load (U.L.) = 40  $\mu$ A HIGH/1.6 mA LOW.

b. The Output LOW drive factor is 2.5 U.L. for Military (XM) and 5 U.L. for Commercial (XC)

Functional Description - The 9401 Cyclic Redundancy Check (CRC) Generator/Checker is a 16-Bit programmable device which operates on serial data streams and provides a means of detecting transmission errors. Cyclic encoding and decoding schemes for error detection are based on polynomial manipulation in modulo arithmetic. For encoding, the data stream (message polynomial) is divided by a selected polynomial. This division results in a remainder which is appended to the message as check bits. For error checking, the bit stream containing both data and check bits is divided by the same selected polynomial. If there are no detectable errors, this division results in a zero remainder. Although it is possible to choose many generating polynomials of a given degree, standards exist that specify a small number of useful polynomials. The 9401 implements the polynomials listed in Table I by applying the appropriate logic levels to the select pins  $S_0$ ,  $S_1$  &  $S_2$ .

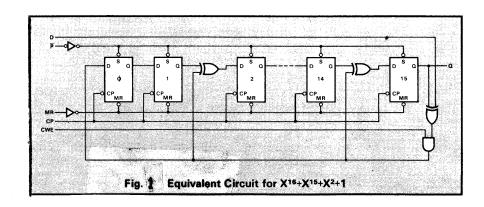

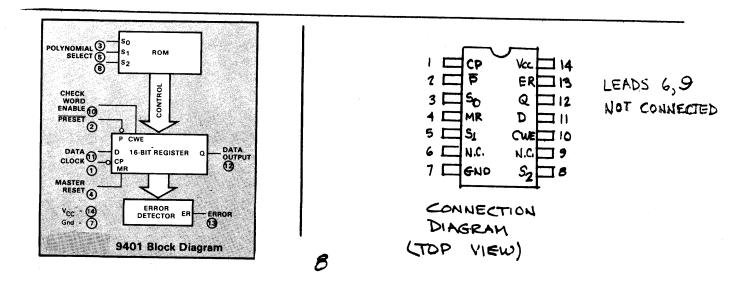

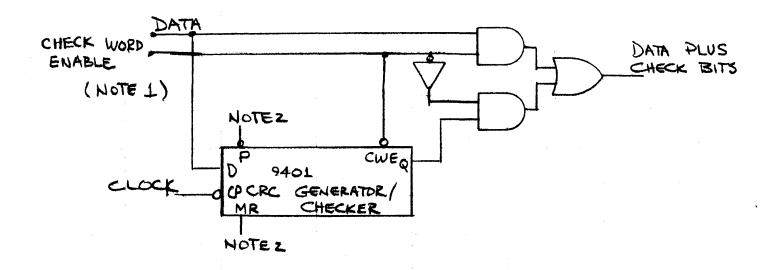

The 9401 consists of a 16-bit register, a Read-Only-Memory (ROM) and associated control circuitry as shown in the Block Diagram. The polynomial control code presented at inputs  $S_0$ ,  $S_1$ , and  $S_2$  is decoded by the ROM, selecting the desired polynomial by establishing shift mode operation on the register with Exclusive OR gates at appropriate inputs. To generate the check bits, the data stream is entered via the Data (D) input, using the HIGH to LOW transition of the Clock  $(\overline{\text{CP}})$  input. This data is gated with the most significant output (Q) of the register, and controls the Exclusive OR gates (Figure 1). The Check Word Enable  $(\overline{\text{CWE}})$  must be held HIGH while the data is being entered. After the last data bit is entered, the  $\overline{\text{CWE}}$  is brought LOW and the check bits are shifted out of the register and appended to the data bits using external gating (Figure 2).

To check an incoming message for errors, both the data and check bits are entered through the D input with the  $\overline{\text{CWE}}$  input held High. The 9401 is not in the data path, but only monitors the message. The Error output becomes valid after the last check bit has been entered into the 9401 by a HIGH to LOW transition of  $\overline{\text{CP}}$ . If no detectable errors have occured during the data transmission, the resultant internal register bits are all LOW and the Error output (ER) is LOW. If a detectable error has occured, ER is HIGH. ER remains valid until the next HIGH to LOW transition of  $\overline{\text{CP}}$  or until the device has been Preset or Reset.

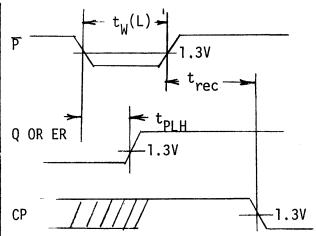

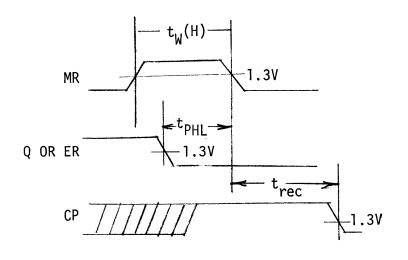

A HIGH level on the Master Reset (MR) input asynchronously clears the register. A LOW level on the Preset  $(\overline{P})$  input asynchronously sets the entire register if the control code inputs specify a 16-bit polynomial; in the case of 12 or 8-bit check polynomials only the most significant 12 or 8 register bits are set and the remaining bits are cleared.

TABLE I

|                | LECT |                | POLYNOMIAL                                                     | REMARKS           |

|----------------|------|----------------|----------------------------------------------------------------|-------------------|

| S <sub>2</sub> | Sı   | ς <sub>0</sub> |                                                                |                   |

| L              | L    | L              | $x^{16}+x^{15}+x^{2}+1$                                        | CRC-16            |

| L              | L    | H              | $x^{16}+x^{14}+x+1$                                            | CRC-16 REVERSE    |

| L              | Н    | L              | $x^{16} + x^{15} + x^{13} + x^{7} + x^{4} + x^{2} + x^{1} + 1$ |                   |

| L              | Н    | Н              | $x^{12}+x^{11}+x^3+x^2+x+1$                                    | CRC-12            |

| Н              | L    | L              | $x^{8}+x^{7}+x^{5}+x^{4}+x+1$                                  |                   |

| Н              | L    | Н              | x <sup>8</sup> +1                                              | LRC-8             |

| Н              | Н    | L              | $x^{16}+x^{12}+x^{5}+1$                                        | CRC-CCITT         |

| Н              | Н    | Н              | $x^{16}+x^{11}+x^{4}+1$                                        | CRC-CCITT REVERSE |

### RECOMMENDED OPERATING CONDITIONS

| PARAMETER                            |     | 9401 XM |     |      |     |      |       |

|--------------------------------------|-----|---------|-----|------|-----|------|-------|

| · AHAMETEN                           | MIN | TYP     | MAX | MIN  | TYP | MAX  | UNITS |

| Supply Voltage V <sub>CC</sub>       | 4.5 | 5.0     | 5.5 | 4.75 | 5.0 | 5.25 | V     |

| Operating Free Air Temperature Range | -55 | 25      | 125 | 0    | 25  | 75   | °c    |

X = package type;

D for Ceramic Dip, P for Plastic Dip.

# DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise noted)

|        |                           |       |         | •      | arriess Offiel | Wise noted   |                                                                                              |  |

|--------|---------------------------|-------|---------|--------|----------------|--------------|----------------------------------------------------------------------------------------------|--|

| SYMBOL | PARAMETER                 |       |         | LIMITS |                |              |                                                                                              |  |

|        |                           |       | MIN TYP |        | MAX            | UNITS        | TEST CONDITIONS (Note 1                                                                      |  |

| VIH    | Input HIGH Voltage        |       | 2.0     |        |                | V            | Guaranteed Innex III Color                                                                   |  |

| VíL ·  | Input LOW Voltage         | XM    |         |        | 0.7            |              | Guaranteed Input HIGH Voltage                                                                |  |

|        |                           | XC    |         |        | 0.8            | \ \ \        | Guaranteed Input LOW Voltage                                                                 |  |

| VCD    | Input Clamp Diode Volta   | ge    |         | ~ 0.65 | -1.5           | V            | V <sub>CC</sub> = MIN, I <sub>IN</sub> = -18 mA                                              |  |

| ∨он I  | Output HIGH Voltage       | XM    | 2.5     | 3.4    | <b>†</b>       | <del> </del> |                                                                                              |  |

|        |                           | XC    | 2.7     | 3.4    |                | \ \ \        | VCC = MIN, IOH = -400 μA                                                                     |  |

| VOL    | Output LOW Voltage        | XM&XC |         | 0.35   | 0.4            | V            | VCC = MIN, IOL = 4.0 mA                                                                      |  |

|        |                           | xc    |         | 0.45   | 0.5            | V            | V <sub>CC</sub> = MIN, I <sub>OL</sub> = 8.0 mA                                              |  |

| iH     | Input HIGH Current        |       |         | 1.0    | 20             | μА           | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 2.7 V                                               |  |

|        | Inn. 4 I OW O             |       |         |        | 0.1            | mA           | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 5.5 V                                               |  |

| IL     | Input LOW Current         |       | _       |        | -0.36          | mA           | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 0.4 V                                               |  |

| os     | Output Short Circuit Curr | ent   | -10     |        | -42            | mA           |                                                                                              |  |

| cc     | Supply Current            |       |         | 70     |                | mA           | V <sub>CC</sub> = MAX, V <sub>OUT</sub> = 0 V (Note 3)<br>V <sub>CC</sub> = MAX, INPUTS OPEN |  |

NOTES

1, CHECK WORD ENABLE IS HIGH WHILE DATA IS BEING CLOCKED,

LOW DURING TRANSMISSION OF CHECK BITS

2. 9401 MUST BE RESET OR PRESET BEFORE EACH COMPUTATION

9401

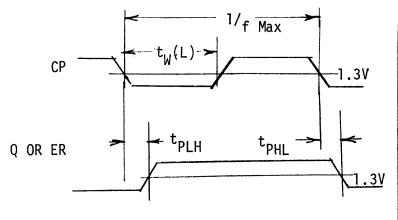

Switching Characteristics ( $T_A = 25$ °C,  $V_{CC} = 5.0$ V)

| CVMDOL                                                   |                                                         |     | LIMITS   |     |       |               |                        |

|----------------------------------------------------------|---------------------------------------------------------|-----|----------|-----|-------|---------------|------------------------|

| SYMBOL                                                   | PARAMETER                                               | MIN | (note 2) | MAX | UNITS | CONI          | DITIONS                |

| fmax                                                     | Maximum Clock Frequency                                 | 12  | 20       |     | MHz   |               |                        |

| TPHL<br>t <sub>PLH</sub> t <sub>PHL</sub>                | Propagation delay, Clock,MR<br>to Data Output           |     | 30       | 55  | ns    | Fig 3         | C <sub>L</sub> = 15 pF |

|                                                          | Propagation delay, Preset to<br>Data Output             |     | 40       | 60  |       | Fig.3,<br>4,5 |                        |

| t <sub>PLH</sub><br>t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation delay,Clock,MR<br>or Preset to Error Output |     | 40       | 60  | ns    |               |                        |

Switching Set-up Requirements ( $T_A = 25$ °C,  $V_{CC} = 5.0$ V)

| SYMBOL                | DADAMETED                                |     | LIMITS |     |       |         |               |

|-----------------------|------------------------------------------|-----|--------|-----|-------|---------|---------------|

|                       | PARAMETER                                | MIN | TYP    | MAX | UNITS | COND    | ITIONS        |

| twCP (L)              | Clock pulse width (LOW)                  | 35  |        |     | ns    | Fig.2   |               |

| t <sub>s</sub> D      | Set-up time, Data to Clock               |     | 35     | 55  | ns    |         |               |

| t <sub>s</sub> CWE    | Set-up time, CWE to Clock                |     | 35     | 55  | ns    | Fig. 6  |               |

| t <sub>h</sub>        | Hold time, Data and CWE to Clock         |     | 0      |     | ns    | 119. 0  | $C_L = 15 pF$ |

| t <sub>w</sub> P (L)  | Preset pulse width (LOW)                 | 35  | 25     |     | ns    | Fig.4   |               |

| t <sub>w</sub> MR (H) | Master Reset pulse width (HIGH)          | 35  | 25     |     | ns    | Fig.6   |               |

| t <sub>rec</sub>      | Recovery time, MR and Preset<br>to Clock |     | 25     | 35  | ns    | Fig.4,5 |               |

#### Notes:

- For conditions shown as MIN or MAX, use appropriate value specified under recommended operating conditions for the applicable device type.

Typical limits are at V<sub>CC</sub>=5.0 V, T<sub>A</sub> = 25°C.

Not more than one output should be shorted at a time.

Fig. 3

PROPAGATION DELAYS, CLOCK

TO Q AND CLOCK TO ER

Fig. 4 PROPAGATION DELAYS,  $\overline{P}$  TO Q AND ER, PLUS RECOVERY TIME  $\overline{P}$  TO CP

Fig. 5

PROPAGATION DELAYS, MR

TO Q AND ER PLUS

RECOVERY TIME, MR TO CP

Fig. 6

SET-UP AND HOLD TIMES,

DATA TO CLOCK AND CWE

TO CLOCK

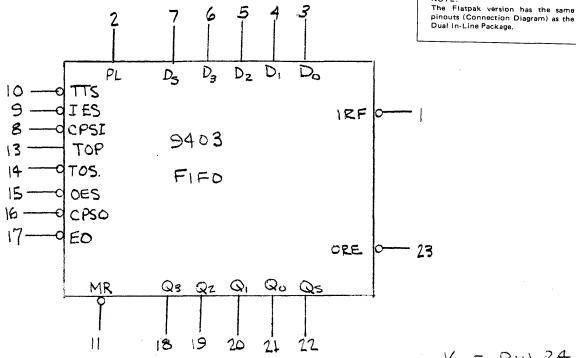

### FAIRCHILD TTL MACROLOGIC\* 9403

DESCRIPTION - The 9403 is an expandable fall-through type high speed First In-First Out (FIFO) buffer memory optimized for high speed disc or tape controllers and communication buffer applications. It is organized as 16 words by 4 bits and may be expanded to any number of words (in multiples of 16) and/or any number of bits (in multiples of 4). Data may be entered or extracted asynchronously in serial or parallel, allowing economical implementation of buffer memories.

Three state outputs are provided for added versatility. The 9403 is a member of Fairchild's TTL Macrologic family and is fully compatible with all TTL families.

# FEATURES 14 MHz serial or parallel data rate Serial or parallel input Serial or parallel output Expandable without external logic Three state outputs Fully compatible with all TTL families 24 pin package

LOGIC SYMBOL

VCC= PIN 24

CONNECTION DIAGRAM

DIP (TOP VIEW)

**□** 23

22

21 20

19

Q<sub>3</sub> 18 EO 17

CPSO 16

ŌĒS 15

TOS 14

2 PL

10 🗖 TTS

11 MR

GHD = PIN 12

| B.             |                                      | Loadir      | ng (note a) |

|----------------|--------------------------------------|-------------|-------------|

|                | LEAD NAMES                           | HIGH (U.L.) | LOW (U.L.)  |

| DO - D3        | Parallel Data Inputs                 | 0.5         | 0.23        |

| DS             | Serial Data Input                    | 0.5         | 0.23        |

| PL             | Parallel Load Input                  | 0.5         | 0.23        |

| CPSI           | Serial Input Clock (operates on      | 0.5         | 0.23        |

| 0131           | negative going transition)           |             |             |

| ĪES            | Serial Input Enable (active LOW)     | 0.5         | 0.23        |

| TTS            | Transfer to Stack Input (active LOW) | 0.5         | 0.23        |

| <del>OES</del> | Serial Output Enable Input (active   | 0.5         | 0.25        |

| 023            | LOW)                                 |             |             |

| TOS            | Transfer Out Serial Input (active    | 0.5         | 0.23        |

| 103            | LOW)                                 |             |             |

| ТОР            | Transfer Out Parallel Input          | 0.5         | 0.23        |

| MR             | Master Reset (active LOW)            | 0.5         | 0.23        |

| EO             | Output Enable (active LOW)           | 0.5         | 0.23        |

| ₹ CPSO         | Serial Output Clock Input (operates  | 0.5         | 0.23        |

| 1 0130         | on negative going transition)        |             | •           |

| 0 - 0          | Parallel Data Outputs                | 130         | 10 (note b) |

| $Q_0 - Q_3$    | •                                    |             |             |

| Qs             | Serial Data Output                   | 10          | 10 (note b) |

| ĪRF            | Input Register Full Output (active   | 10          | 5 (note b)  |

|                | LOW)                                 |             | 5 ( , , , ) |

| ORE            | Output Register Empty Output (active | 10          | 5 (note b)  |

|                | LOW)                                 |             |             |

# NOTES:

- a) 1 unit load (U.L.) = 40  $\mu\text{A}$  HIGH, 1.6 ma LOW.

- b) Output fanout with VOL $\leq$  0.5 volts.

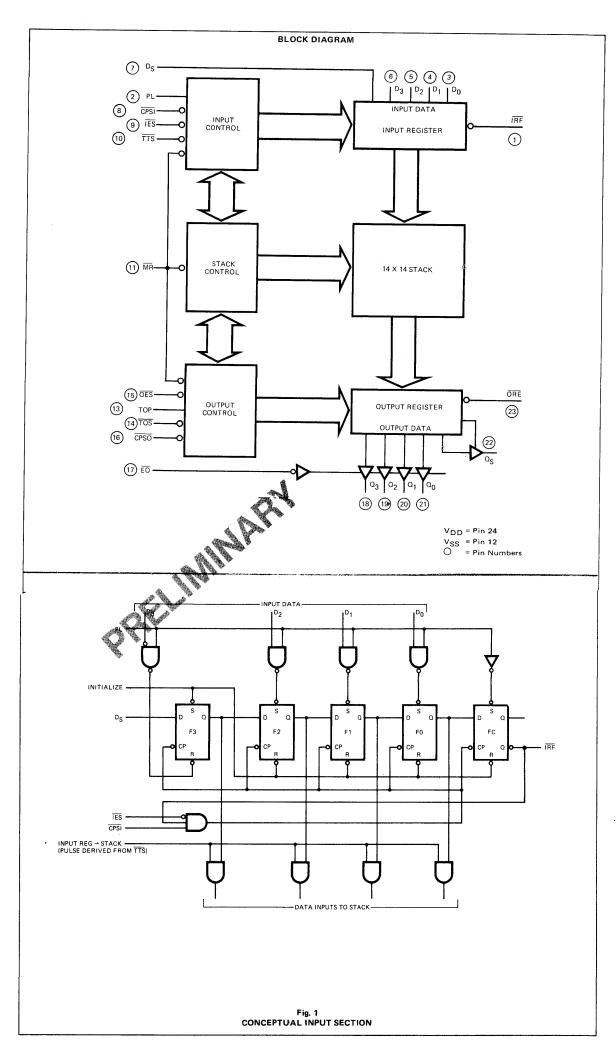

FUNCTIONAL DESCRIPTION - As shown in the block diagram the 9403 consists of three parts:

- 1. an input register with parallel and serial data inputs as well as control inputs and outputs for input handshaking and expansion.

- 2. a four bit wide, 14 word deep fall-through stack with self-contained control logic.

- 3. an output register with parallel and serial data outputs as well as control inputs and outputs for output handshaking and expansion.

Since these three sections operate asynchronously and almost independently, they will be described separately below:

#### INPUT REGISTER (DATA ENTRY):

The input register can receive data in either bit-serial or in 4-bit parallel form, store it until it is sent to the fall-through stack, and generate and accept the necessary status and control signals.

Figure 1 is a conceptual logic diagram of the input section. As described later, this five bit register is initialized by setting the F3 flip-flop and resetting the other flip-flops. The  $\overline{\mathbb{Q}}$  output of the last flip-flop (FC) is brought out as the "input Register Full" output ( $\overline{\text{IRF}}$ ). After initialization this output is High.

#### PARALLEL ENTRY:

A High level on the PL input loads the DO - D3 data inputs into the FO - F3 flip-flops and sets the FC flip-flop, which forces  $\overline{\text{IRF}}$  LOW, indicating "input register full". The D inputs must be stable while PL is HIGH. During parallel entry, the  $\overline{\text{IES}}$  input should be LOW; the  $\overline{\text{CPSI}}$  input may be either HIGH or LOW.

#### SERIAL ENTRY:

Data on the DS input is serially entered into the  $F_3$ ,  $F_2$ ,  $F_1$ ,  $F_0$ , FC shift register on each HIGH-to-LOW transition of the  $\overline{CPSI}$  clock input, provided  $\overline{IES}$  and PL are LOW.

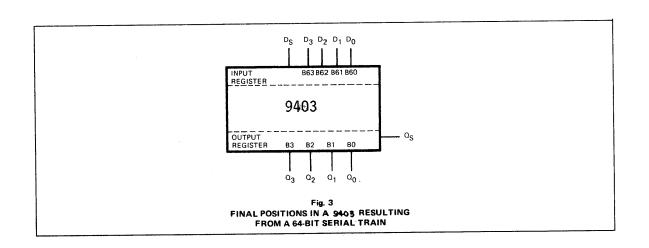

After the fourth clock transition the four serial data bits are aligned in the four data flip-flops and the FC flip-flop is set, forcing  $\overline{\text{IRF}}$  LOW (input register full) and internally inhibiting further  $\overline{\text{CPSI}}$  clock pulses. Figure 2 illustrates the final positions in a 9403 resulting from a 64-bit serial bit train. BO is the first bit, B63 the last bit.

#### TRANSFER TO THE FALL-THROUGH STACK:

The outputs of flip-flops FO - F3 feed the Stack. A LOW level on the TTS input attempts to initiate a "fall-through" action. If the top location of the Stack is empty, data is loaded into the Stack and the input register is re-initialized. Note that this initialization is postponed until PL is LOW again. Thus, automatic FIFO action is achieved by connecting the  $\overline{\text{IRF}}$  output to the  $\overline{\text{TTS}}$  input.

Data falls through the Stack automatically, pausing only when it is necessary to wait for an empty next location. In the 9403 like in most modern FIFO designs the  $\overline{\text{MR}}$  input initializes the Stack control section only and does not clear the data.

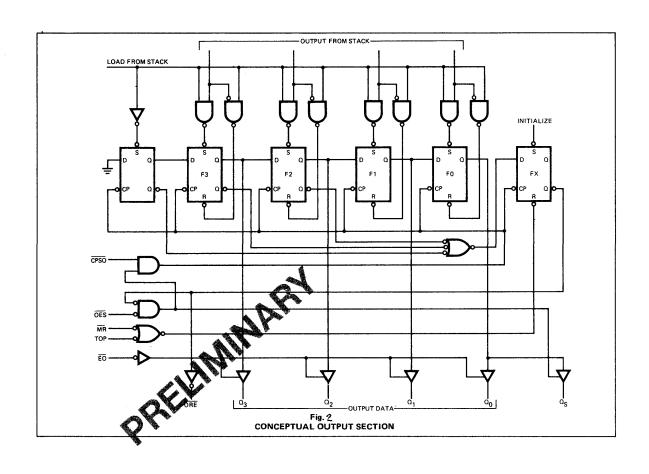

#### **OUTPUT REGISTER (DATA EXTRACTION):**

The output register receives four-bit data words from the bottom Stack location, stores it and outputs data on a 3-state four-bit parallel data bus or on a 3-state serial data bus. The output section generates and receives the necessary status and control signals. Figure 3 is a conceptual logic diagram of the output section.

#### PARALLEL DATA EXTRACTION:

When the FIFO is empty after a LOW pulse is applied to  $\overline{\text{MR}}$ , the Output Register Empty ( $\overline{\text{ORE}}$ ) output is LOW. After data has been entered into the FIFO and has fallen through to the bottom Stack location, it is transferred into the output register, provided the "Transfer Out Parallel" (TOP) input is HIGH, and the  $\overline{\text{OES}}$  input is LOW. As a result of the data transfer  $\overline{\text{ORE}}$  goes HIGH, indicating valid data on the data outputs (provided the 3-state buffer is enabled). TOP can now be used to clock out the next word. When TOP goes LOW,  $\overline{\text{ORE}}$  will go LOW indicating that the output data has been extracted, but the data itself remains on the output bus until the next LOW-to-HIGH transition of TOP transfers the next word (if available) into the output register as explained above. During parallel data extraction,  $\overline{\text{TOS}}$ ,  $\overline{\text{CPSO}}$ , and  $\overline{\text{OES}}$  should be LOW.

#### SERIAL DATA EXTRACTION:

When the FIFO is empty after a LOW pulse is applied to  $\overline{\text{MR}}$ , the Output Register Empty  $(\overline{\text{ORE}})$  output is LOW. After data has been entered into the FIFO and has fallen through to the bottom Stack location, it is transferred into the output shift register provided the "Transfer Out Serial"  $(\overline{\text{TOS}})$  is LOW. TOP must be HIGH, and  $\overline{\text{OES}}$  and  $\overline{\text{CPSO}}$  must be LOW. As a result of the data transfer  $\overline{\text{ORE}}$  goes HIGH indicating valid data in the shift register. The 3-state serial data output Qs is automatically enabled and puts the first data bit on the output bus. Data is serially shifted out on the HIGH-to-LOW transition of  $\overline{\text{CPSO}}$ . The fourth transition empties the shift register, forces  $\overline{\text{ORE}}$  LOW and disables the serial output Qs. For serial operation

the  $\overline{\text{ORE}}$  output may be tied to the  $\overline{\text{TOS}}$  input, requesting a new word from the Stack as soon as the previous one has been shifted out.

#### **EXPANSION:**

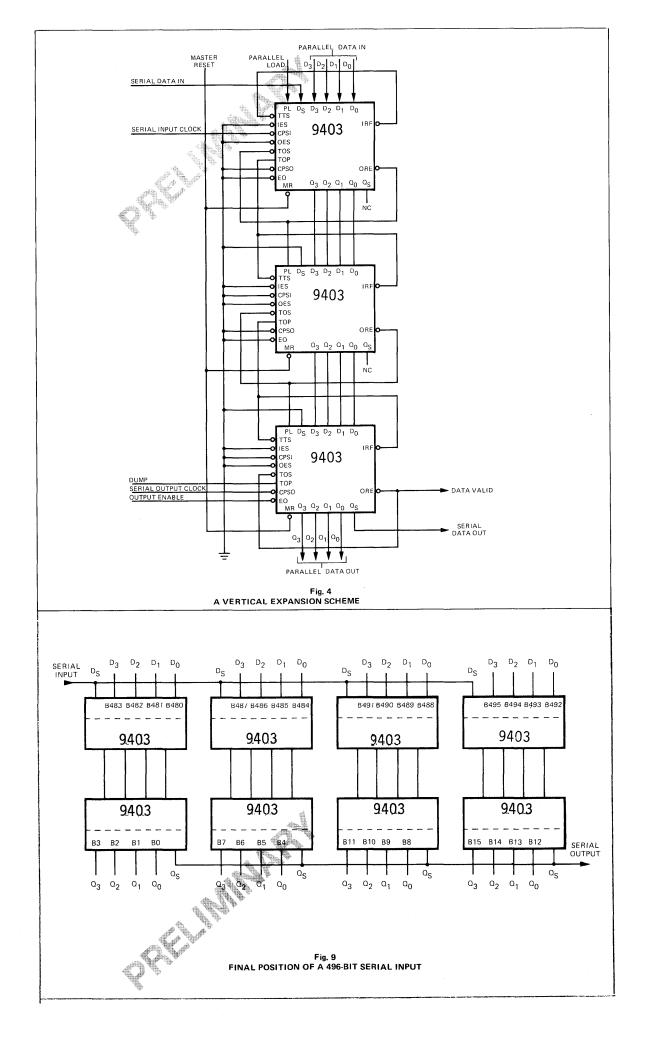

<u>Vertical Expansion</u> - The 9403 may be vertically expanded to store more words without external parts. The interconnections necessary to form a 48-word by 4-bit FIFO are shown in Figure 4. Using the same technique, any FIFO of 15N + 1 words by 4 bits can be constructed. Note that expansion does not sacrifice any of the FIFO's flexibility for Serial/Parallel input and output.

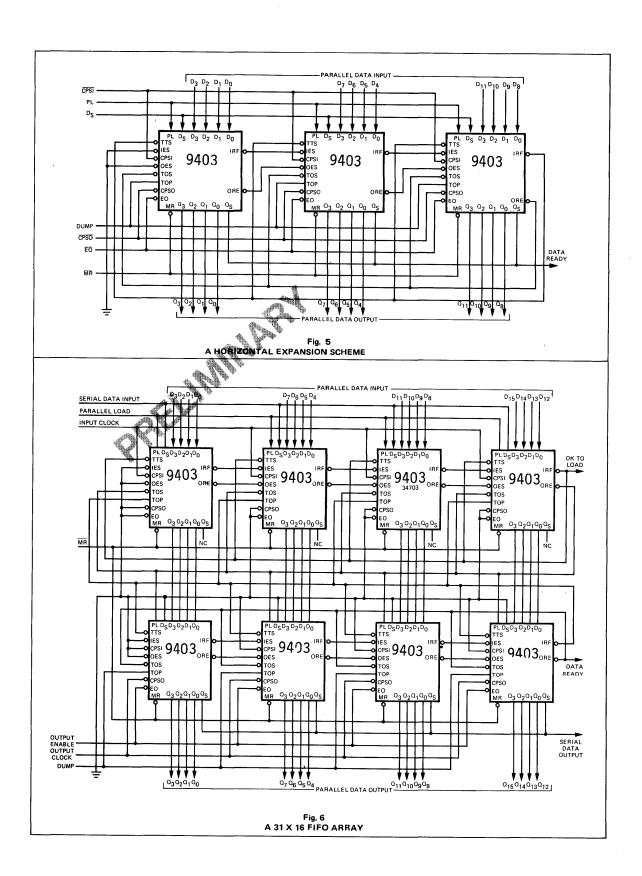

Horizontal Expansion - The 9403 may also be horizontally expanded to store long words (in multiples of 4 bits) without external logic. The interconnections necessary to form a 16-word by 12-bit FIFO are shown in Figure 5. Using the same technique, any FIFO of 16 words by 4 X N bits can be constructed. When expanding in the horizontal direction, it is usual to connect the  $\overline{\text{IRF}}$  and  $\overline{\text{ORE}}$  outputs of the right most device (most significant device) to the  $\overline{\text{TTS}}$  and  $\overline{\text{TOS}}$  inputs respectively of all devices to the left (less significant devices) to guarantee that no operation is initiated before all devices are ready.

As in the vertical expansion scheme, horizontal expansion does not sacrifice any of the FIFO's flexibility for Serial/Parallel input and output.

<u>Horizontal and Vertical Expansion</u> - The 9403 can be expanded in both the horizontal and vertical direction without any external parts and without sacrificing any of the FIFO's flexibility for Serial/Parallel input and output. The interconnections necessary to form a 32-word by 16-bit FIFO are shown in Figure 6. Using the same technique, any FIFO of  $15N_1$  + 1 words by 4 X  $N_2$  bits can be constructed.

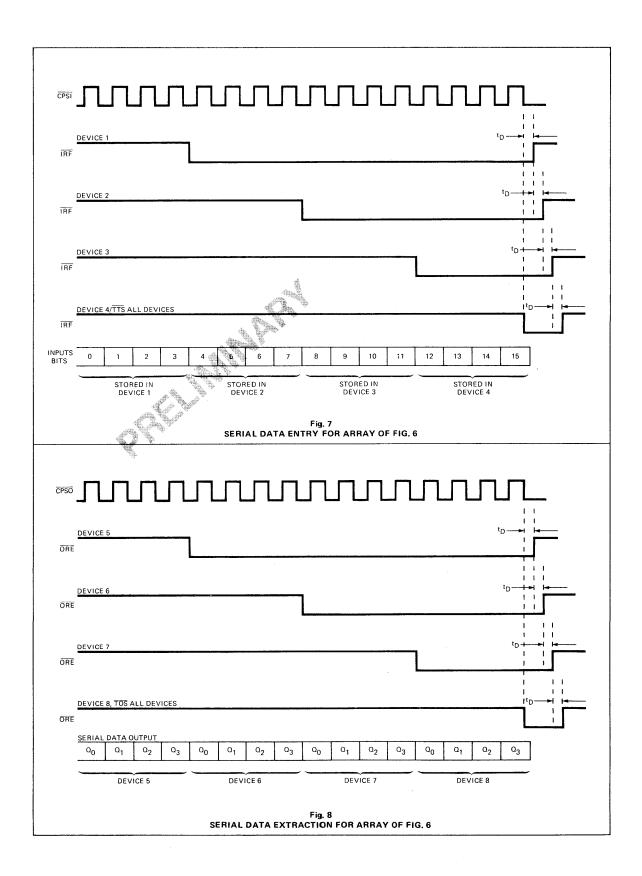

Figures 7 and 8 show the timing diagrams for serial data entry and extraction for the 32-word by 16-bit FIFO shown in Figure 6. The final position of data after serial insertion of 496 bits into the FIFO array of Figure 6 is shown in Figure 9.

#### INTERLOCKING CIRCUITRY:

Most conventional FIFO designs provide status signals analogous to  $\overline{\text{IRF}}$  and  $\overline{\text{ORE}}$ ; however, when these devices are operated in arrays, variations in unit to unit operating speed require external gating to assure all devices have completed an operation. The 9403 incorporates simple but effective "Master-Slave" interlocking circuitry to eliminate the need for external gating.

In the 9403 array of Figure 6 Devices 1 and 5 are defined as "Row Masters" and the other devices are slaves to the Master in their row. No slave in a given row will initialize its input register until it has received LOW on its  $\overline{\text{IES}}$  input from a

Row Master or a Slave of higher priority.

In a similar fashion, the  $\overline{\text{ORE}}$  outputs of slaves will not go HIGH until their  $\overline{\text{OES}}$  input has gone HIGH. This interlocking scheme ensures that new input data may be accepted by the array when the  $\overline{\text{IRF}}$  output of the final slave goes LOW and that output data for the array may be extracted when the  $\overline{\text{ORE}}$  of the final slave in the output row goes HIGH.

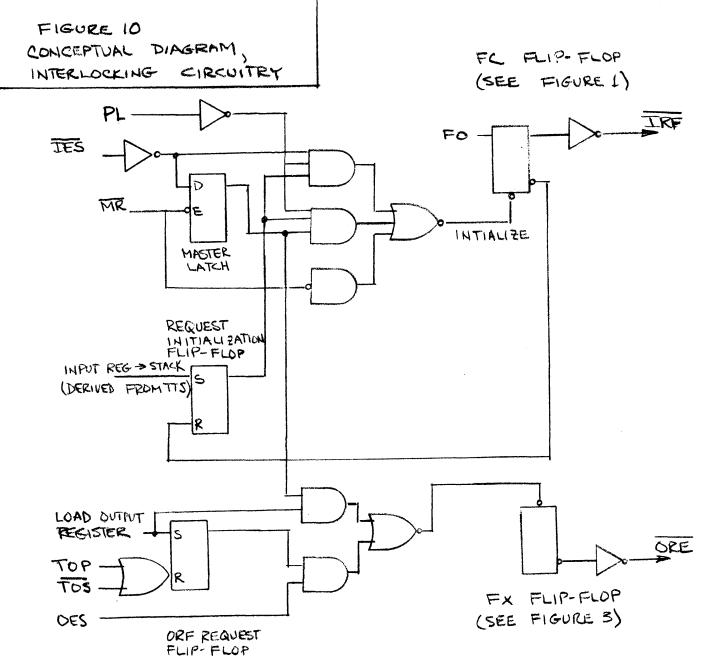

The Row Master is established by connecting its  $\overline{\text{IES}}$  input to ground while a slave receives its  $\overline{\text{IES}}$  input from the  $\overline{\text{IRF}}$  output of the next higher priority device. When an array of 9403 FIFOs is initialized with a LOW on the  $\overline{\text{MR}}$  inputs of all devices, the  $\overline{\text{IRF}}$  outputs of all devices will be HIGH. Thus, only the Row Master receives a LOW on the  $\overline{\text{IES}}$  input during initialization. Figure 10 is a conceptual logic diagram of the internal circuitry which determines Master–Slave operation. Whenever  $\overline{\text{MR}}$  and  $\overline{\text{IES}}$  are low, the Master latch is set. Whenever  $\overline{\text{TTS}}$  goes LOW the Request Initialization flip-flop will be set. If the Master latch is HIGH, the input register will be immediately initialized and the Request Initialization flip-flop reset. If the Master latch is reset, the input register is not initialized until  $\overline{\text{IES}}$  goes LOW. In array operation, activating the  $\overline{\text{TTS}}$  initiates a ripple input register initialization from the Row Master to the last Slave.

A similar operation takes place for the output register. Either a  $\overline{10S}$  or  $\overline{10P}$  input initiates a load-from-stack operation and sets the  $\overline{ORE}$  Request flip-flop. If the Master latch is set, the last output register flip-flop is set, and  $\overline{ORE}$  goes HIGH. If the Master latch is reset, the  $\overline{ORE}$  output will be LOW until an  $\overline{OES}$  input is received.

Table 1 summarizes Master-Slave status outputs.

| OUTPUT CONDITION | INTERNAL                                       | STATE                                  |

|------------------|------------------------------------------------|----------------------------------------|

|                  | Master Operation -<br>IES LOW when initialized | Slave Operation -<br>IES HIGH when ini |

|                  |                                                |                                        |

TABLE 1

itialized Input Register Full and IES IRF LOW Input Register Full Output Register not full & OES LOW ORE LOW Output Register not full

#### DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise noted)

| SYMBOL          | PARAMETE                                 | В                         |      |      | LIMIT | S              |       | ] ,,,,     | ıTC              | TEST CONDITIONS (N. v. 4)                                                                          |  |

|-----------------|------------------------------------------|---------------------------|------|------|-------|----------------|-------|------------|------------------|----------------------------------------------------------------------------------------------------|--|

| 31WBUL          | FARAWETER                                |                           |      | N    | TYP M |                | MAX   | UNITS      |                  | TEST CONDITIONS (Note 1)                                                                           |  |

| V <sub>IH</sub> | Input HIGH Voltage                       |                           | 2    | .0   |       |                |       | \<br> <br> | ,                | Guaranteed Input HIGH Voltage                                                                      |  |

| v <sub>IL</sub> | Input LOW Voltage                        | XM                        |      |      |       |                | 0.7   |            | ,                | Guaranteed Input LOW Voltage                                                                       |  |

|                 | xc xc                                    |                           | -    |      |       | _              | 0.8   |            |                  |                                                                                                    |  |

| V <sub>CD</sub> | Input Clamp Diode Volta                  |                           |      |      | -0.65 |                | -1.5  | \ \        | <u>'</u>         | V <sub>CC</sub> = MIN, I <sub>IN</sub> = -18 mA                                                    |  |

| Vон             | Output HIGH Voltage                      | XM                        |      | .5   | 3.4   |                |       | - V        | , . ·            | VCC = MIN, IOH = -400 μA.                                                                          |  |

|                 | QS, ORE, OES                             | xc                        |      | .7   | 3.4   |                |       | ļ          |                  |                                                                                                    |  |

| ∕он ∣           | Output HIGH Voltage                      | XM                        |      | 4    | 3.4   | _              |       | ٧          | _                | IOH = - 2.0 MA VCC = MIN                                                                           |  |

| <del></del>     | Qo, Q, Oz, Q                             | XC T                      | 2    | 4    | 3.1   | <del>ب</del> ا |       |            |                  |                                                                                                    |  |

| OL              | Output LOW Voltage<br>Qo, ହା, Qz, Q૩, Q૬ | •                         |      | -    | 0.25  | -              | 0.4   |            |                  | V <sub>CC</sub> = MIN, I <sub>OL</sub> = 8.0 mA                                                    |  |

|                 | (40) (41) (42) (43) (43                  | l                         |      | . L_ | 0.35  | 25             | 0.5   | īv         | <del>-  </del>   | V <sub>CC</sub> = MIN, I <sub>OL</sub> = /6, mA<br>I <sub>OL</sub> = 4.0 mA V <sub>CC</sub> = MIN, |  |

| VOL             | Output LOW Voltage                       | ì                         | +    |      | 0.3   |                | 0.5   | v          |                  | 10L = 8.0 mA                                                                                       |  |

|                 | Output Off Current HIGI                  | + Go, Q1, Q2, 4           | 3.64 |      | -     |                | 50    | μA         |                  | VCC = MAX., VOUT = 2.4 V, VE = 0.8                                                                 |  |

| -               | Output Off Current LOW                   | Q0,Q1,Q2,Q3               | 95   |      |       |                | -50   | μΑ         | . i              | V <sub>CC</sub> = MAX., V <sub>OUT</sub> = 0.5 V, V <sub>E</sub> = 0.8                             |  |

| IH              | Input HIGH Current (Ex                   |                           |      |      | 1.0   |                | 20    | μ,         | ١ .              | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 2.7 V                                                     |  |

|                 | (C)                                      | CEFT DES)                 |      |      |       | $oxed{oxed}$   | 0.1   | m          | 4                | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 5.5 V                                                     |  |

| Н               | INPUT HIGH Current,                      |                           |      |      | 2.0   |                | 40    | м          | A                | VCC = MAX, VIN = 2.7V                                                                              |  |

| · ·             | [                                        | OE3                       |      |      |       |                | 0.1   | m          | A                | VCC= MAK, VIN = 5.5V                                                                               |  |

| IIL             | Input LOW Current                        |                           |      |      |       |                | n     | ıΑ         | V <sub>C</sub>   | C = MAX, V <sub>IN</sub> = 0.4 V                                                                   |  |

|                 | ALL EXCEPT                               | OES                       |      |      |       | -0.3           | 6     |            |                  |                                                                                                    |  |

|                 | OES                                      |                           |      |      | l     | - 0.8          | 36    |            | }                |                                                                                                    |  |

| los             | Output Short Circuit C                   | urrent                    | -10  | -    |       | -4             | 2   1 | ıA         | V-               | C = MAX, V <sub>OUT</sub> = 0.0 V                                                                  |  |

|                 | Qs- ORE, CES                             |                           | -    |      | 1     | •              | _   " | \          | \ v <sub>C</sub> | C - MAA, VOUT = 0.0 V                                                                              |  |

| los             | Output Short Circuit Co                  | irrent <i>ଦିର, ଦି</i> । 🖓 | 3 -3 | 30   | 1     |                | -100  | Tr         | nA               | VCC = MAX, VOUT = U V (Note 3)                                                                     |  |

| Icc ·           | Supply Current                           |                           |      |      | 95    |                | 150   |            | nA               | VCC = MAX INPUTS OPEN                                                                              |  |

#### NOTES:

For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type.

Typical limits are at V<sub>CC</sub> = 5.0 V, T<sub>A</sub> = 25°C.

Not more than one output should be shorted at a time.

$V_{CC} = 5v$ ,  $T_{A} = 25^{\circ}C$ ,  $C_{L} = 15 pF$

|   | SYMBOL                               | PARAMETER                                                   |     | LIMITS |     |       | COMMENTS                                                                                            |

|---|--------------------------------------|-------------------------------------------------------------|-----|--------|-----|-------|-----------------------------------------------------------------------------------------------------|

|   |                                      |                                                             | MIN | TYP    | MAX | UNITS | COMPLETE                                                                                            |

|   | t <sub>PHL</sub>                     | Propagation Delay, negative going<br>CP to IRF Output       |     | 16     |     | ns    | Stack not full PL LOW                                                                               |

|   | <sup>t</sup> PLH                     | Propagation Delay, negative going TTS to IRF                |     |        |     | ns    | Figure 11 & 12                                                                                      |

|   | t <sub>PLH</sub><br>t <sub>PHL</sub> | <u>Prop</u> agation Delay, negative going CPSO to Qs Output |     | 25     |     | ns    | Serial Output<br>OES LOW, TOP HIGH<br>Figure 13 & 14                                                |

| 7 | t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay, positive going TOP to Outputs QO-Q3      |     |        |     | ns    | EO, CPSO LOW<br>Figure 15                                                                           |

|   | <sup>t</sup> PHL                     | Propagation Delay, negative going CPSO to ORE               |     |        |     | ns    | Serial Output <del>OES</del><br>LOW, TOP HIGH<br>Figure 13 & 14                                     |

|   | t <sub>PLH</sub>                     | Propagation Delay, positive going TOS to ORE                |     |        |     | ns    |                                                                                                     |

|   | t <sub>PHL</sub>                     | Propagation Delay, negative going TOP to ORE                |     |        |     | ns    | Parallel Output, EO, CPSO LOW                                                                       |

|   | t <sub>PLH</sub>                     | Propagation Delay, positive going TOP to ORE                |     |        |     | ns    | Figure 15                                                                                           |

|   | t <sub>FT</sub>                      | Fall Through Time                                           |     | 300    |     | ns    | TTS connected to <u>IRF</u> TOS connected to <u>ORE</u> IES, OES, EO, CPSO LOW TOP HIGH - Figure 16 |

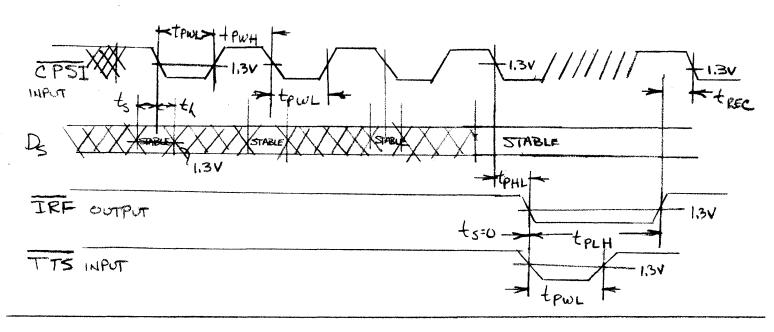

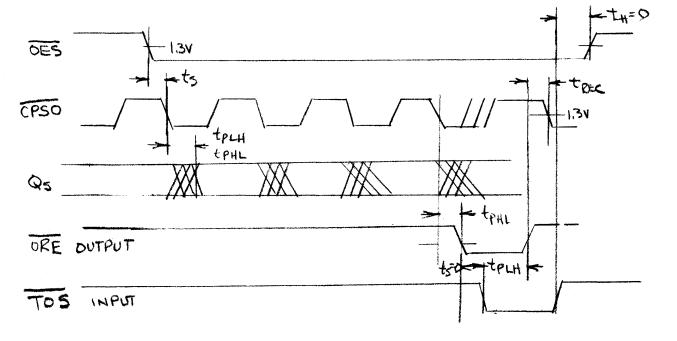

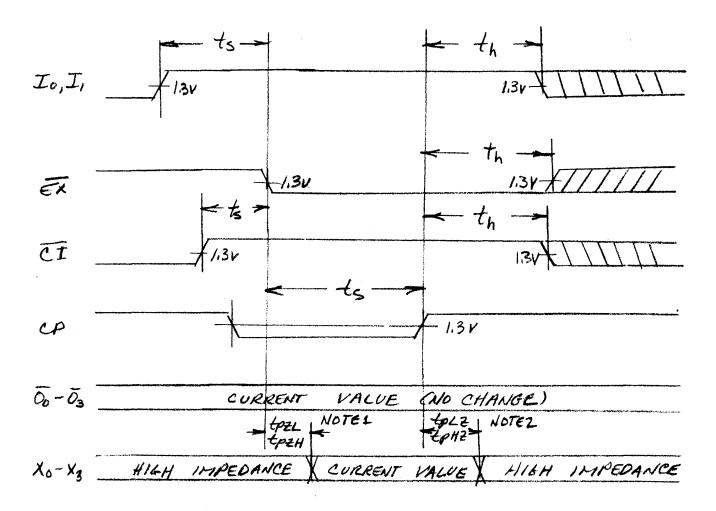

FIGURE 11

SERIAL INPUT: UNEXPANDED OR MASTER OPERATION

CONDITIONS - STACK NOT FULL, TES, PL LULI

FIGURE 12 SERIAL INPUT, EXPANDED SLAVE OPERATION, CONDITIONS! STACK NOT FULL, TES HIGH WHEN INITALIZED, PL LOW

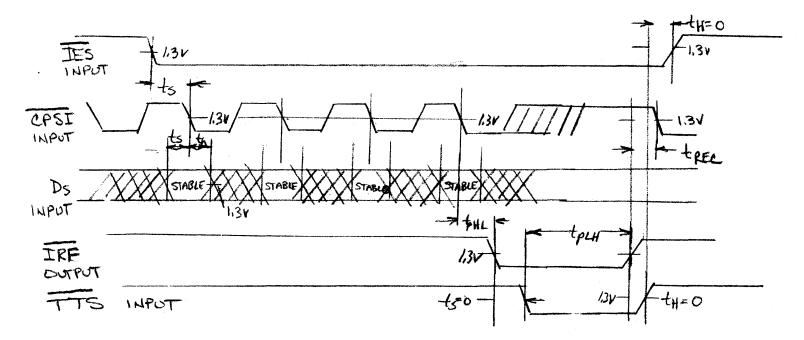

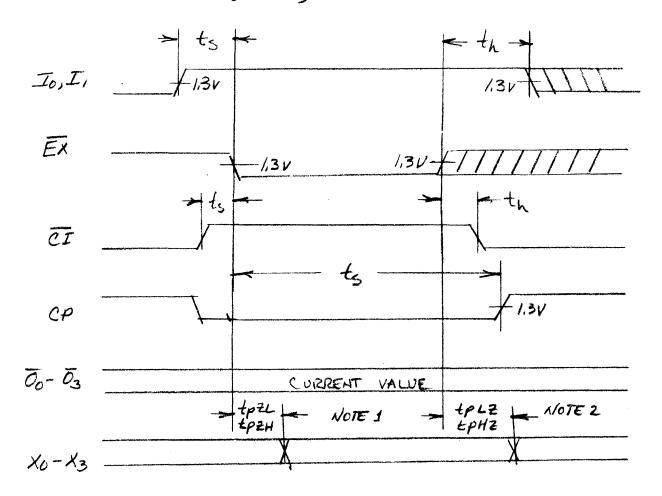

SERIAL OUTPUT, UNEXPANDED OR MASTER OPERATION COMPITIONS! DATA IN STACK, TOP HIGH, TES LOW WHEN INITALIZED, DES LOW

FIGURE 14 DERIAL OUTPUT, SLAVE OPERATION

CONDITIONS: DATA IN STACK, TOP. HIGH, TES

HIGH WHEN INITALIZED.

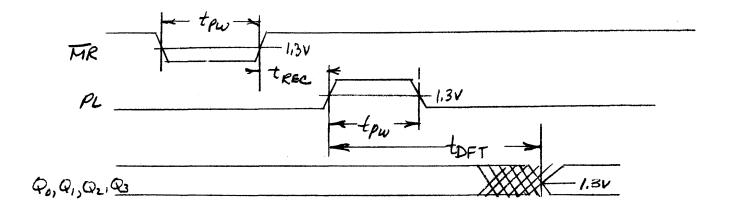

# FIGURE 16

# FALL THROUGH TIME

CONDITIONS: TTS CONNECTED TO IRF TOS CONNECTED TO ORF.

TES, DES, EO, CPSO LOW. TOP HIGH

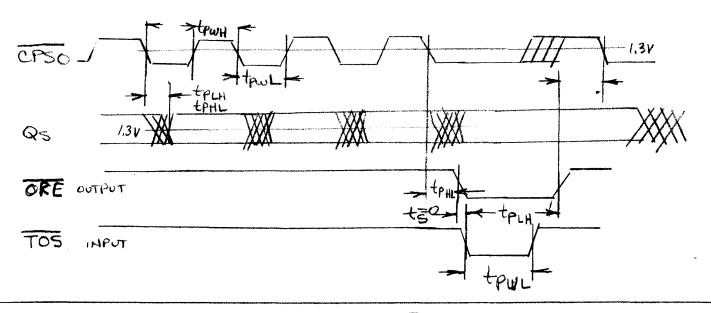

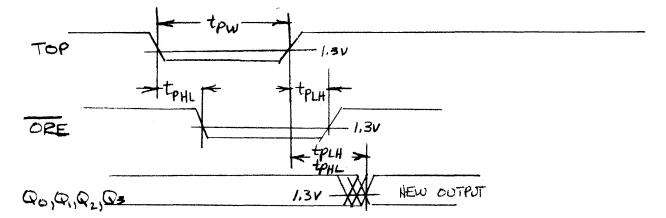

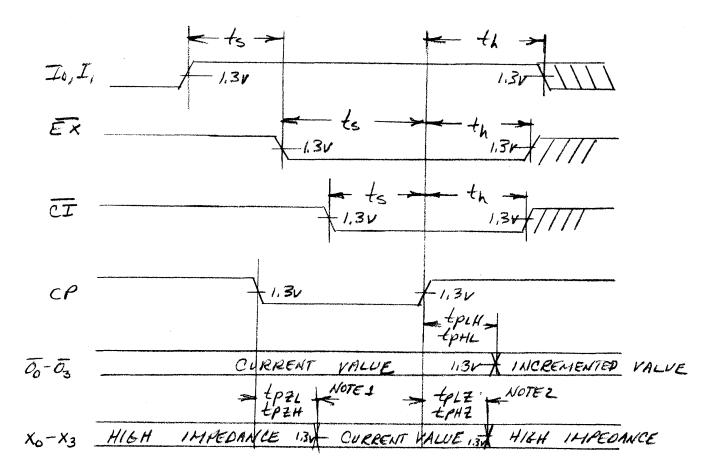

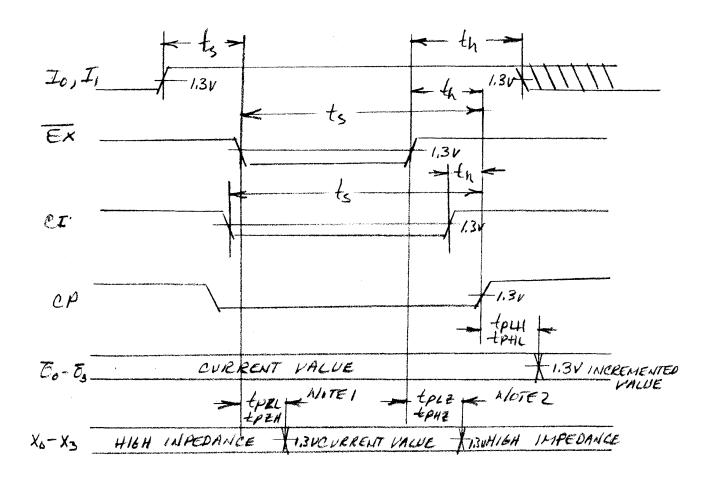

# FIGURE 15

PARALLEL OUTPUT, FOUR BIT WORD OR

MASTER IN PARALLEL EXPANSION

CONDITIONS IES LOW WHEN INITALIZED, EO CPSO LOW.

DATA AVAILABLE IN STACK

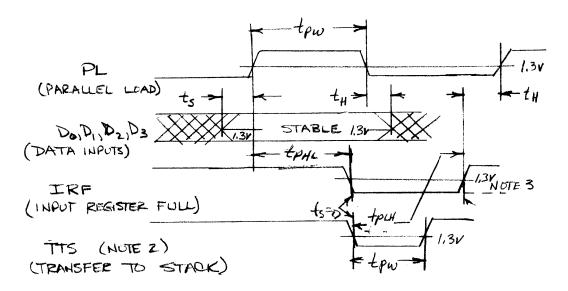

PARALLEL LOAD MODE, FOUR BIT WORD (UNEXPANDED) PARALLEL EXPANSION CONDITIONS: STACK NOT FULL, IES LOW WHEN INITALIZED

#### NOTES!

- 1. INITIALIZATION REQUIRES A MASTER RESET TO OCCURE AFTER POWER HAS BEEN APPLIED.

- Z. TTS HORMALLY CONNECTED TO TRE

- 3, IF STACK IS FULL, TRE WILL STAY LOW

PARALLEL LOAD, SLAVE MODE

CONDITIONS: STACK NOT FULL, DEVICE INITIALIZED (NOTE 1)

WITH TES HIGH

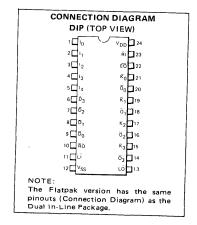

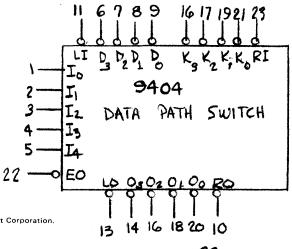

# FAIRCHILD TTL MACROLOGIC\* 9404 DATA PATH SWITCH

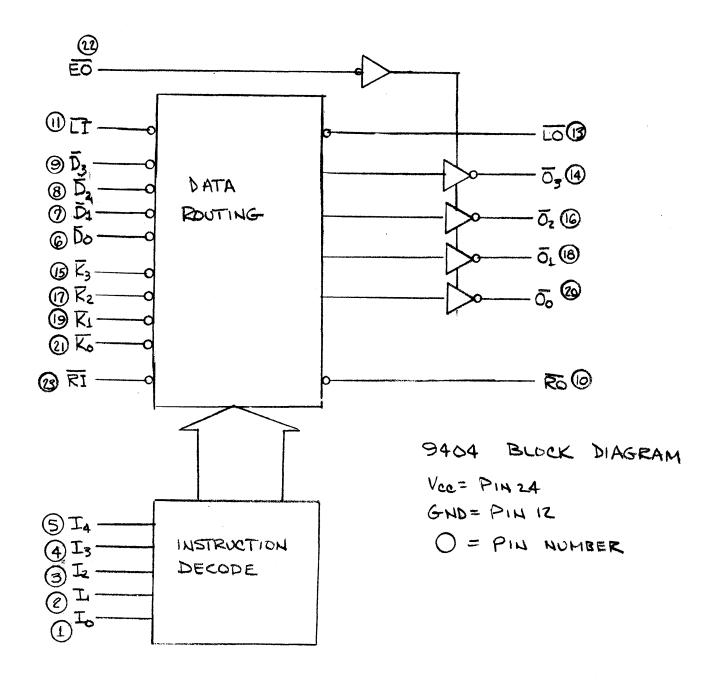

DESCRIPTION - The 9404 Data Path Switch (DPS) is a combinatorial array for closing data path loops around arithmetic/logic networks such as the 9405 (Arithmetic Logic Register Stack). A total of 30 instructions (see Table 1) facilitate logic shifting, masking, sign extension, introduction of common constants and other operations.

The 5-bit Instruction Word  $(I_0-I_4)$  selects one of the thirty instructions operating on two sets of 4-bit Data Inputs  $(\overline{D}_0-\overline{D}_3,\overline{K}_0-\overline{K}_3)$ . Left Input  $(\overline{LI})$  and Left Output  $(\overline{LO})$  and Right Input  $(\overline{RI})$  and Right Output  $(\overline{RO})$  are available for expansion in 4-bit increments. An active LOW Output Enable Input  $(\overline{EO})$  provides 3-state control of the Data Outputs  $(\overline{O}_0-\overline{O}_3)$  for bus oriented applications.

The 9404 is a member of Fairchild's Macrologic family and is fully compatible with all TTL families.

#### **FEATURES**

- Expandable in multiples of four bits

- 30 ns delay over 16-bit word

- Two 4-bit data input buses

- 4-Bit data output bus with 3-state output buffers

- Useful for byte masking and swapping

- Provides arithmetic or logic shift

- Provides for sign extension

- Generates commonly used constants

- Purely combinatorial no clocks required

- Packaged in slim 24 pin package

Vcc = PIN 24 GND = PIN 12

LOGIC SYMBOL

| PIN NAMES                                             |                                  | LOADING (note a) |             |  |  |  |  |

|-------------------------------------------------------|----------------------------------|------------------|-------------|--|--|--|--|

| FIN NAMES                                             |                                  | HIGH (U.L.)      | LOW (U.L.)  |  |  |  |  |

| <u>D</u> 0 - D3                                       | D-Bus Inputs (active LOW)        | 0.5              | 0.23        |  |  |  |  |

| $\overline{K}_0 - \overline{K}_3$                     | K-Bus Inputs (active LOW)        | 0.5              | 0.23        |  |  |  |  |

| <sup>I</sup> <sub>0</sub> - <sup>I</sup> <sub>4</sub> | Instruction Word Input           | 0.5              | 0.23        |  |  |  |  |

| LΤ                                                    | Shift Left Input (active LOW)    | 0.5              | 0.23        |  |  |  |  |

| <del>LO</del>                                         | Shift Left Output (active LOW)   | 10               | 5 (note b)  |  |  |  |  |

| RI                                                    | Shift Right Input (active LOW)   | 0.5              | 0.23        |  |  |  |  |

| RO                                                    | Shift Right Output (active LOW)  | 10               | 5 (note b)  |  |  |  |  |

| <del>E</del> 0                                        | Output Enable Input (active LOW) | 0.5              | 0.23        |  |  |  |  |

| <u>0</u> 0- <u>0</u> 3                                | Data Output (active LOW)         | 130              | 10 (note b) |  |  |  |  |

### NOTES:

- a) l unit load (U.L.) = 40 μΑ HIGH, 1.6 ma LCW

- b) Output current measured at  $V_{OUT} = 0.5V$

TABLE 1 INSTRUCTION SET FOR THE 9404

| Γ. | INPUTS OUTPUTS INDUTE OUTPUTS |     |    |    |                  |                  |                  |                  |                         |    |    |     |    |     |                  |                           |                  |                  |                  |     |                            |

|----|-------------------------------|-----|----|----|------------------|------------------|------------------|------------------|-------------------------|----|----|-----|----|-----|------------------|---------------------------|------------------|------------------|------------------|-----|----------------------------|

| -  | ''                            | VPU | 15 |    | OUTPUTS          |                  |                  |                  | FUNCTION                |    |    | NPU |    |     | OUTPUTS          |                           |                  |                  |                  |     | <b>5</b> .                 |

| 14 | lз                            | 12  | 11 | 10 | 03               | 02               | 01               | O <sub>0</sub>   |                         | 14 | l3 | 12  | 11 | 10  | LO               | ō3                        | ō2               | Ō <sub>1</sub>   | ō <sub>0</sub>   | RO  | FUNCTION                   |

| L  | L                             | L   | L  | L  | L                | L                | L                | L                | Byte Mask               | н  | L  | L   | L  | L   | RI               |                           |                  |                  |                  |     | K-Bus Sign Extend          |

| -  | L                             | L   | L  | Н  | Н                | Н                | Н                | Н                | Byte Mask               | Н  | L  | L   | L  | Н   | ₹ <sub>3</sub>   | K <sub>3</sub>            | $\overline{K}_2$ | $\overline{K}_1$ | $\bar{\kappa}_0$ |     | K-Bus Sign Extend          |

|    | L                             | L   | Н  | L  | L                | L                | L                | Н                | Minus "2" in 2s Comp(1) | н  | L  | L   | Н  |     |                  | ŘΙ                        |                  |                  |                  |     | D-Bus Sign Extend          |

| _  | L                             | L   | Н  | Н  | L                | L                | L                | L                | Minus "1" in 2s Comp(1) | н  | L  | L   | Н  | н   | $\overline{D}_3$ | $\overline{D}_3$          | $\overline{D}_2$ | $\overline{D}_1$ | $\overline{D}_0$ |     | D-Bus Sign Extend          |

| L  | L                             |     | L  |    | $\overline{D}_3$ | $\bar{D}_2$      | $\overline{D}_1$ | $\overline{D}_0$ | Byte Mask D-Bus         | Н  | L  | Н   | L  | L   |                  | $\overline{D}_2$          |                  |                  |                  |     | D-Bus Shift Left           |

| ᅵㄴ | L                             | Н   | L  | Н  | Н                | Н                | Н                | Н                | Byte Mask D-Bus         | н  | Ĺ  | Н   | L  | н   |                  | $\bar{K}_2$               |                  |                  |                  |     | K-Bus Shift Left           |

| L  | L                             | Н   | Н  | L  | $\overline{D}_3$ | $\overline{D}_2$ | $\overline{D}_1$ | $\overline{D}_0$ | Byte Mask D-Bus         | н  | L  | н   | Н  |     | ٦                |                           |                  |                  |                  | Īο  | D-Bus Shift Right          |

| L  | L                             | Н   | Н  | H  | L                | L                | L                | L                | Byte Mask D-Bus         | Н  | L  | Н   | Н  | н   |                  | $\overline{\mathtt{D}}_3$ |                  |                  |                  |     | D-Bus Shift Right Arith(2) |

| L  | Н                             | L   | L  | L  | L                | Н                | Н                | н                | Negative Byte Sign Mask | Н  | Н  | L   | L  | L   |                  |                           |                  |                  |                  | -   | K-Bus Shift Right          |

| L  | Н                             | L   | L  | Н  | н                | Н                | Н                | н                | Positive Byte Sign Mask | н  | н  | L   | L  | н   |                  |                           |                  |                  |                  |     | K-Bus Shift Right Arith(2) |

| L  | Н                             | L   | н  | L  | ĸ̄3              | $\bar{\kappa}_2$ | $\bar{\kappa}_1$ | Κ̈́o             | Byte Mask K-Bus         | н  | н  |     | н  | - 1 |                  | K <sub>3</sub>            |                  |                  |                  |     | Byte Mask K-Bus            |

| L  | Н                             | L   | Н  | н  | L                | L                | L                | L                | Byte Mask K-Bus         | н  | Н  | L   | Н  | н   |                  | _                         | H                | H                | -                |     | Byte Mask K-Bus            |

| L  | Н                             | Н   | L  | L  | $\bar{D}_3$      | $\overline{D}_2$ | $\overline{D}_1$ | D <sub>0</sub>   | Load Byte               | н  | н  | Н   | L  | L   |                  | D <sub>3</sub>            |                  |                  |                  | - 1 | Complement D-Bus           |

| L  | Н                             | Н   | L  | н  | $\overline{K}_3$ | $\bar{\kappa}_2$ | $\bar{\kappa}_1$ | $\bar{\kappa}_0$ | Load Byte               | Н  | н  |     |    | н   |                  | K3                        | _                | •                | •                | - 1 | Complement K-Bus           |

| L  | H,                            | Н   | Н  | L  | н                | н                | Н                |                  | Plus "1"                | н  | н  | Н   | Н  |     |                  | 3                         | 2                |                  | 0                | - 1 | Undefined                  |

| L  | Н                             | Н   | Н  | Н  | н                | Н                | Н                | Н                | Zero                    | н  | н  | Н   |    | н   |                  |                           |                  |                  |                  |     | Undefined                  |

H = HIGH Level

L = LOW Level

(1) Comp = Complement (2) Arith = Arithmetic

#### Description

The 9404 Data Path Switch combines the functions of a dual four-input multiplexer, a true/complement one/zero generator, and a shift left/shift right array.

As shown in Table 1, there are two shift right modes. The arithmetic right shift preserves the sign bit in the most significant position while the logic shift moves all positions. Right shift is defined as a one-bit shift toward the least significant position.

For half word arithmetic the 9404 provides instructions which extend the sign bit left through the more significant slices. Shift linkages are available as individual inputs and outputs for complete flexibility.

The 9404 may be used to generate constants +1, 0, -1 and -2 in two's complement notation.

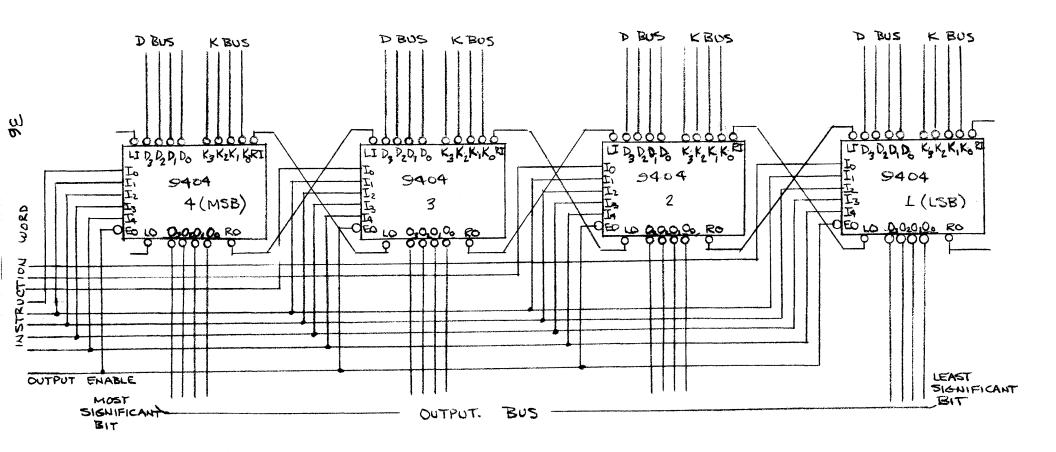

#### 9404 ARRAYS

Arrays of larger than 4-bit word lengths are easily obtained. Figure 1 illustrates a 16-bit array constructed using 4 devices; device 1 is the least significant and device 4 is the most significant slice. Within each slice, inputs and outputs with '0' subscript are the least significant bits.

The  $I_1$  through  $I_4$  inputs of all devices are bussed. These four bus lines together with the  $I_0$  inputs of the devices form an 8-bit instruction bus to control the array. In some applications, it may be possible to connect the  $I_0$  inputs of devices 1 & 2 together and the  $I_0$  inputs of devices 3 & 4 together, so that only 6 bits are needed to control the arrays. Connecting the  $\overline{L0}$  of device 1 to  $\overline{RI}$  of device 2,  $\overline{L0}$  of device 2 to  $\overline{RI}$  of device 3, etc. provides left shift (i.e., shift towards most significant bit) and sign extension. From Table 1 it can be seen that "sign extend" consists of two adjacent instructions differing only in  $I_0$ ; one of these instructions connects the most significant bit of the selected input bus (i.e.,  $D_3$  or  $K_3$ ) to the  $\overline{L0}$  output while the other instruction forces the output bus and  $\overline{L0}$  to the  $\overline{RI}$  input. In a similar fashion right shift operation is accomplished by connecting the  $\overline{L1}$  input of a device to the  $\overline{R0}$  of the next more significant device.

FIGURE L 16 BIT 9404 ARRAY

#### DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise noted)

| 0.41001              | BARAMETER                             |           |                    | LIMITS |       | UNITS | TEST CONDITIONS (Note 1)                         |  |

|----------------------|---------------------------------------|-----------|--------------------|--------|-------|-------|--------------------------------------------------|--|

| SYMBOL               | PARAMETE                              | PARAMETER |                    | TYP    | MAX   | UNITS |                                                  |  |

| v <sub>iH</sub>      | Input HIGH Voltage                    |           | t HIGH Voltage 2.0 |        |       | V     | Guaranteed Input HIGH Voltage                    |  |

| <br>VíL              | Input LOW Voltage                     | XM        |                    |        | 0.7   | V     | Guaranteed Input LOW Voltage                     |  |

| VIL                  | Input LOW Voltage                     | XC        |                    |        | 0.8   |       | Cuaranteed input LOW Voltage                     |  |

| V <sub>CD</sub>      | Input Clamp Diode Volta               | ge        |                    | -0.9   | -1.5  | V     | V <sub>CC</sub> = MIN, I <sub>IN</sub> = -18 mA  |  |

| \/a                  | Output UICH Voltage                   | XM        | 2.5                | 3.4    |       | V     | Vac = MIN 10 = 4004                              |  |

| Voн                  | Output HIGH Voltage                   | XC        | 2.7                | 3.4    |       | ]     | $V_{CC} = MIN, I_{OH} = -400 \mu\text{A},$       |  |

| Voн                  |                                       |           | 2.4                | 3.4    |       |       | 10H = -2.0 mA VCC = MIN                          |  |

| *UH                  | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | YO        | 2.4                | 3.1    |       |       | 10H=-5.2 mA                                      |  |

| ЮН                   | Output HIGH Current                   |           |                    |        | 100   | μΑ    | V <sub>CC</sub> = MIN, V <sub>OH</sub> = 5.5 V,  |  |

|                      |                                       |           |                    | 0.3    | 0.4   | V     | V <sub>CC</sub> = MIN, I <sub>OL</sub> = 4.0 mA, |  |

| VOL                  | Output LOW Voltage                    | Lo, Ro    |                    | 0, 4   | 0.5   | V     | V <sub>CC</sub> = MIN, I <sub>OL</sub> = 8.0 mA, |  |

|                      |                                       |           |                    | 0.3    | 0.4   | v     | VCC = MIN, IOL = 8.0 mA,                         |  |

| VoL                  | Output LOW Voltage                    | ō₀ - Ō₃   |                    | 0.4    | 0.5   | V     | VCC = MIN, IOL = 16 mA,                          |  |

|                      | Output Off Current HIG                | H         |                    |        | 50    | μΑ    | VCC = NAX., VOUT 12 V. VC 0.63                   |  |

| '07 <u>Н</u><br>Чиль | Output Off Current LOW                |           |                    |        | -50   | μ 1   | Voca MAX., Your 15 V, Vr 31                      |  |

|                      | Input HIGH Current                    |           | T                  | 1.0    | 20    | μА    | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 2.7 V   |  |

| ин                   |                                       |           |                    |        | 0.1   | mÁ    | VCC = MAX, VIN = 5.5 V                           |  |

|                      | Input LOW Current                     |           |                    |        | -0.36 | mA    | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 0.4 V   |  |

|     | Output Short Circuit Current | -30 | -100 | mA | V <sub>CC</sub> = MAX, V <sub>OUT</sub> = 0 V (Note 3) |

|-----|------------------------------|-----|------|----|--------------------------------------------------------|

| los | Supply Current               |     |      | mA | VCC = MAX, INFOT, OPEN                                 |

#### NOTES:

<sup>1.</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable

device type.

2. Typical limits are at V<sub>CC</sub> = 5.0 V, T<sub>A</sub> = 25° C.

3. Not more than one output should be shorted at a time.

## SWITCHING CHARACTERISTICS

$V_{CC} = 5V$ , TA = 25°C,  $C_L = 15$  pF

|                  | DOI.     | PARAMETER                                                                                                               |     | IMITS |     | UNITS | COMMENTS |

|------------------|----------|-------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|-------|----------|

| SYM              | BUL      | FARAPICIER                                                                                                              | MIN | TYP   | MAX |       |          |

| t <sub>PLI</sub> | H        | Propagation Delay, Data Inputs                                                                                          |     | 20    |     | ns    |          |

| t <sub>PHI</sub> | L.       | $(\overline{D}_0 - \overline{D}_3, \overline{K}_0 - \overline{K}_3)$ to Output $(0_0 - 0_3)$                            |     |       |     |       |          |

| t <sub>PLI</sub> | Н        | Propagation Delay, Data Inputs                                                                                          |     | 18    |     | ns    |          |

| t <sub>PHI</sub> | L        | $(\overline{D}_0 - \overline{D}_3, \overline{K}_0 - \overline{K}_3)$ to Shift Outputs $\overline{LO}$ , $\overline{RO}$ |     |       |     |       |          |

| t <sub>PLI</sub> | Н        | Propagation Delay, $\overline{RI}$ to $\overline{LO}$                                                                   |     | 8     |     | ns    | EO LOW   |

| t <sub>PHI</sub> | L        | Propagation Delay, RI to LU                                                                                             |     |       |     |       |          |

| t <sub>PLI</sub> | Н        | Propagation Delay, Instruction word                                                                                     |     | 00    |     | ns    |          |

| t <sub>PHI</sub> | L        | $(I_0 - I_5)$ to Data Outputs $(\overline{0}_0 - \overline{0}_3)$                                                       | •   | 22    |     |       |          |

| t <sub>PLI</sub> | H        | Propagation Delay, Instruction word                                                                                     |     |       |     | ns    |          |

| t <sub>PHI</sub> | <u> </u> | (I <sub>0</sub> -I <sub>5</sub> ) to Shift Outputs RO, LO                                                               |     | 20    |     |       |          |

| t <sub>PZI</sub> | H        | Enable Delay, EO to Outputs                                                                                             |     | 10    |     | ns    |          |

| t <sub>PZI</sub> | L        | $\overline{0}_0 - \overline{0}_3$                                                                                       |     | 10    |     |       |          |

| t <sub>PL</sub>  | Z        | Disable Delay FO to 0                                                                                                   |     | _     |     | ns    |          |

| t <sub>PH</sub>  | Z        | Disable Delay, $\overline{E0}$ to $\overline{0_0}$ - $\overline{0_3}$                                                   |     | 5     |     |       |          |

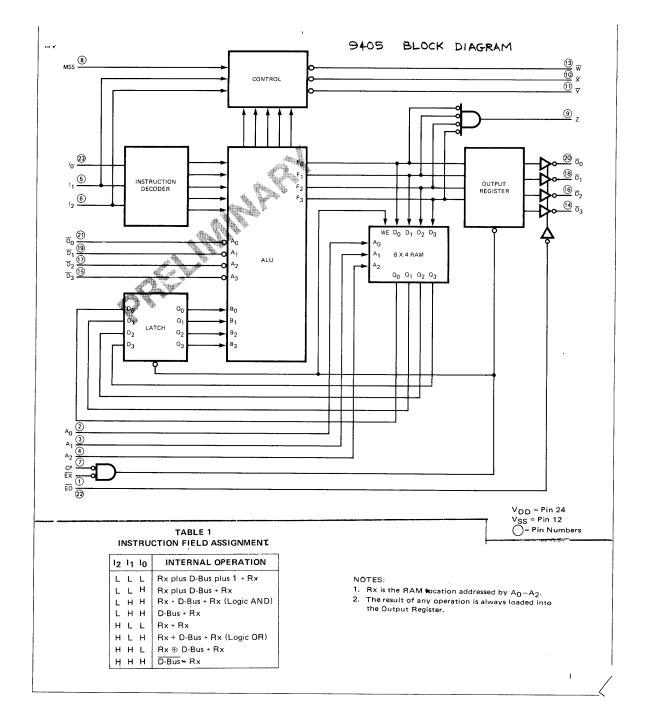

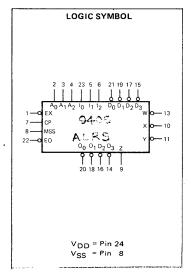

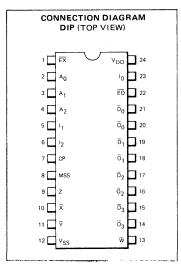

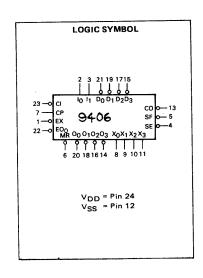

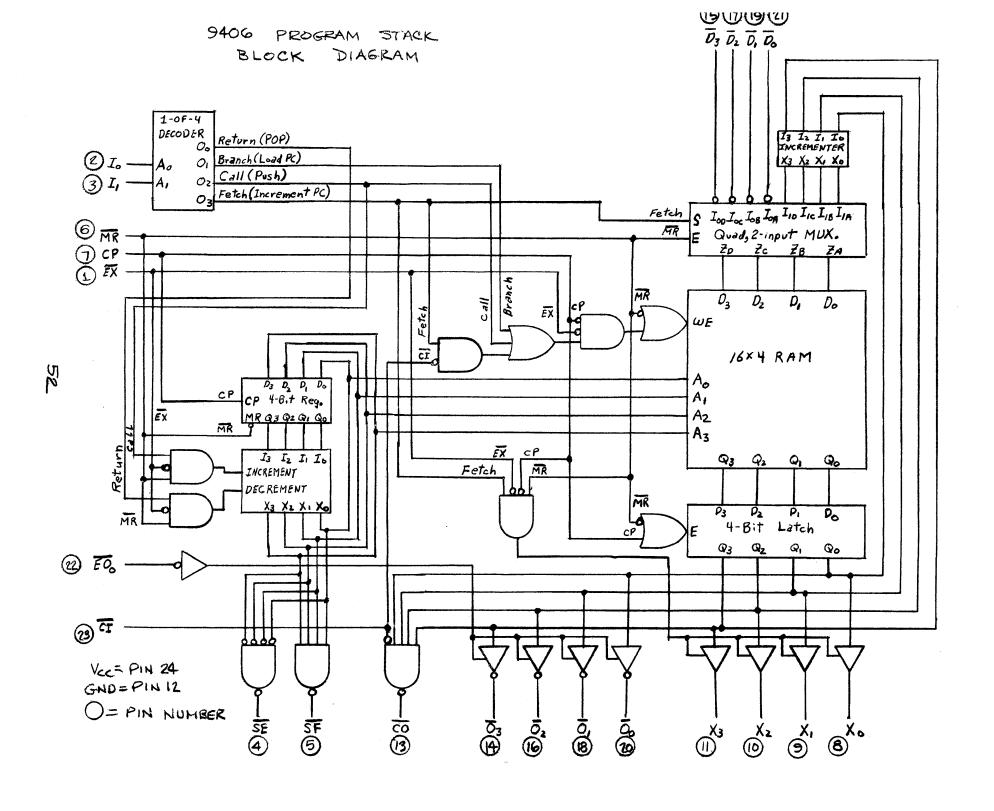

#### FAIRCHILD TTL MACROLOGIC\* 9405

#### Arithmetic Logic Register Stack

#### **DESCRIPTION**

The Arithmetic Logic Register Stack (ALRS) is designed to implement general registers in high performance programmable digital systems. The device contains a 4-bit arithmetic logic unit (ALU), an 8 word by 4-bit RAM, and associated control logic. The ALU implements 8 arithmetic and logic functions where one 4-bit operand is supplied from an external source (input data bus) and the second 4-bit operand is supplied internally from one of the 8 RAM words selected by the Address Inputs  $(A_0-A_2)$ . The result of the operation is loaded into the same RAM location and simultaneously, is loaded into the output register making it available at the 3-state output data bus.

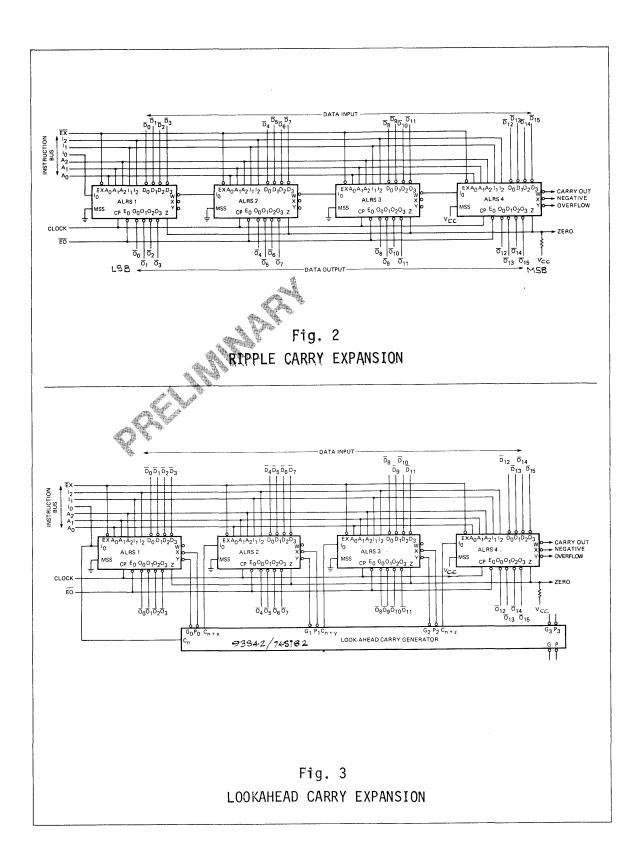

The 9405 operates on four bits of data but features are provided for expansion to longer word lengths. Carry Propagate & Carry Generate outputs are provided for an external carry lookahead where maximum operating speed is required. In applications where high speed arithmetic is not needed, ripple expansion may also be implemented. The 9405 provides three status signals Zero, Negative and Overflow to qualify the result of an operation. The 9405 is a member of Fairchild's Macrologic family and is fully compatible with all TTL families.

#### **FEATURES**

- Eight general registers/accumulators in a single package

- High speed 10 MHz Microinstruction rate

- Expandable in multiples of 4 bits

- Provides for ripple or lookahead carry

- Implements 64 microinstructions

- Provides status zero, negative, and overflow

- Three state outputs

- 24 pin package

<sup>\*</sup>A Trademark of Fairchild Camera and Instrument Corporation.

| LEAD NAMES                        |                                                     | LOADING (r | note a)   |

|-----------------------------------|-----------------------------------------------------|------------|-----------|

| LEAD NAMES                        |                                                     | HIGH(U.L.) | LOW(U.L.) |

| <u>D</u> 0 - D3                   | Data Inputs (active LOW)                            | 0.5        | 0.23      |

| A <sub>0</sub> - A <sub>2</sub>   | Address Instruction Inputs                          | 0.5        | 0.23      |

| I <sub>0</sub> - I <sub>2</sub>   | ALU Instruction Inputs (note b)                     | 0.5        | 0.23      |

| MSS                               | Most Significant Slice Input (active HIGH)          | 0.5        | 0.23      |

| СР                                | Clock Input                                         | 0.5        | 0.23      |

| EO                                | Output Enable Input (active LOW)                    | 0.5        | 0.23      |

| EX                                | Execute Input (active LOW)                          | 0.5        | 0.23      |

| $\overline{0}_0 - \overline{0}_3$ | Data Outputs (active LOW)                           | 130        | 10        |

| W                                 | Ripple Carry Output (active LOW) (note c)           | 10         | 5         |

| $\overline{X}$                    | Carry Propagate Output (note d)                     | 10         | 5         |

| Ϋ́                                | Carry Generate Output (note e)                      | 10         | 10        |

| Z                                 | Zero Status Output (active HIGH, Open<br>Collector) | (note f)   | 5         |

|                                   |                                                     |            |           |

#### NOTES:

- a) 1 unit load (U.L.) = 40  $\mu$ a HIGH, 1.6 ma LOW (0.5V).

- b)  $\ \mathbf{I}_{0}$  used also for Carry Input on lesser significant slices.

- c)  $\overline{\mathtt{W}}$  Output also carries instruction information.

- d)  $\overline{X}$  Output provides Negative Status (active LOW) on most significant slice.

- e)  $\overline{Y}$  Output provides Overflow Status (active LOW) on most significant slice.

- f) An external pull-up resistor is required to supply HIGH level drive capability.

FUNCTIONAL DESCRIPTION - As shown in the Block Diagram the 9405 Arithmetic Logic Register Stack (ALRS) consists of a 4-bit ALU, an 8-word by 4-bit RAM with output latches, an instruction decode network, control logic, and a 4-bit Output Register.

The ALU receives the active LOW input data  $(\overline{D}_0 - \overline{D}_3)$  as one operand while the RAM provides the second operand through latches. The ALU output is stored in both the RAM and output register. The active LOW output data bus  $(\overline{0}_0 - \overline{0}_3)$  is obtained from the output register through 3-state buffers. An active LOW Output Enable  $(\overline{E0})$  input controls these buffers; a HIGH level on  $\overline{E0}$  disables them (high impedance state).

The instruction bus for the 9405 consists of two fields, A and I;  $A_0$  -  $A_2$  specify the desired location of the RAM and  $I_0$  -  $I_2$  specify the desired function to be performed. Table 1 lists Instruction Field Code assignments. Thus, the 9405 provides eight registers ( $R_0$  -  $R_7$ ) and eight different operations may be performed on any of these registers. The  $I_0$  -  $I_2$  inputs are decoded by the instruction decode network to generate necessary control signals for the ALU. The ALU also generates and transmits to the control logic the following signals: Carry Out, Carry Propagate, Carry Generate, Negative Status and Overflow Status. The control logic manipulates the status signals as a function of  $I_0$  -  $I_2$  and a control input MSS. A HIGH level on the MSS input declares the most significant slice in a 9405 array (the diode-input on MSS allows it to be tied directly to  $V_{CC}$ ). All devices, except the most significant 9405 should have a LOW level (ground) on the MSS input. The control logic generates three device outputs,  $\overline{W}$ ,  $\overline{X}$  and  $\overline{Y}$  for arrayed operation. An all zero result from the ALU is decoded and presented at the open collector Zero Status (Z) Output.

The  ${\rm I}_0$  input serves a dual purpose: for arithmetic instructions, it is used as the carry input and for non-arithmetic instructions it serves as an instruction input. This is possible because only two arithmetic instructions require carry. The dual purpose use of  ${\rm I}_0$  plays an important role in 9405 expansion schemes.

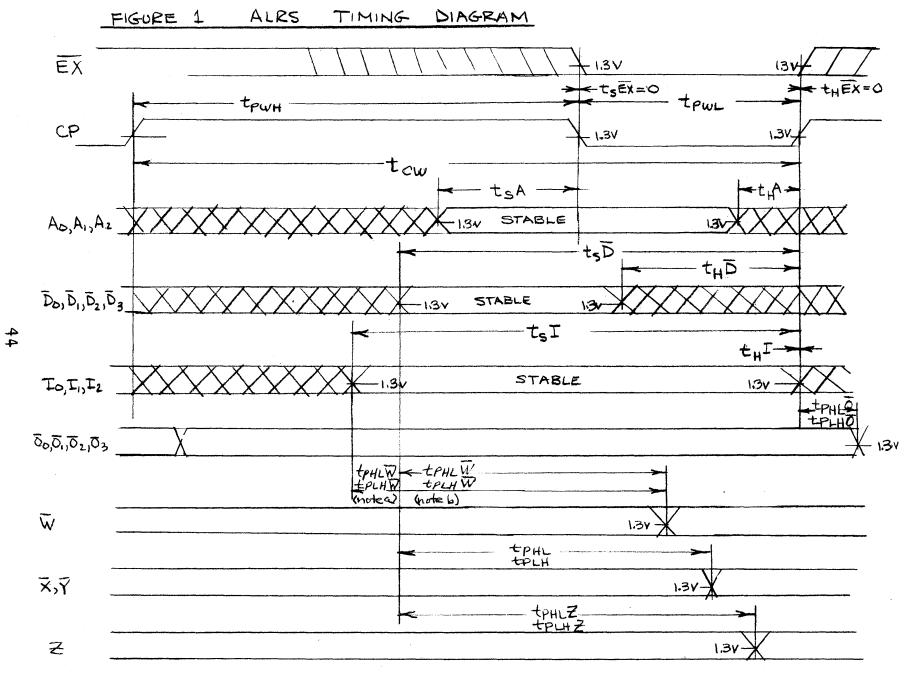

OPERATION - The 9405 operates on a single clock. CP and  $\overline{\text{EX}}$  are inputs to a 2-input active LOW AND gate. A microcycle starts as the clock goes HIGH. For normal operation the Execute ( $\overline{\text{EX}}$ ) is LOW. Data is read from the RAM through enabled latches and applied as one operand to the ALU. Data inputs ( $\overline{\text{D}}_0$  -  $\overline{\text{D}}_3$ ) are applied to the ALU as the other operand and the operation as determined by instruction lines  $I_0$  -  $I_2$  is executed. When CP is LOW, the latches are disabled and the result of the operation is written back into the RAM provided that  $\overline{\text{EX}}$